SCL Products

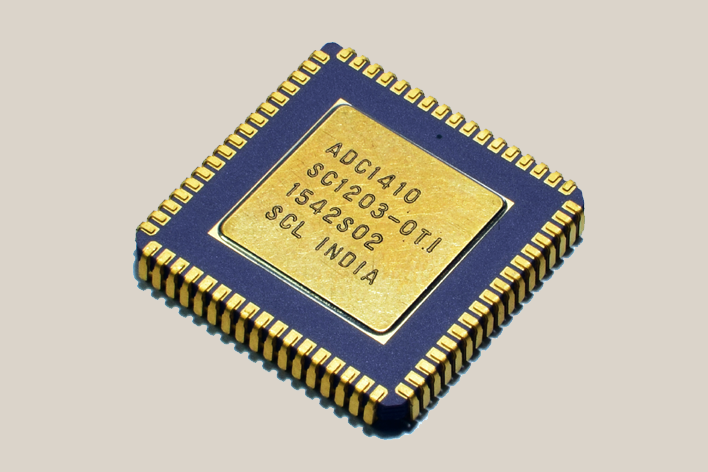

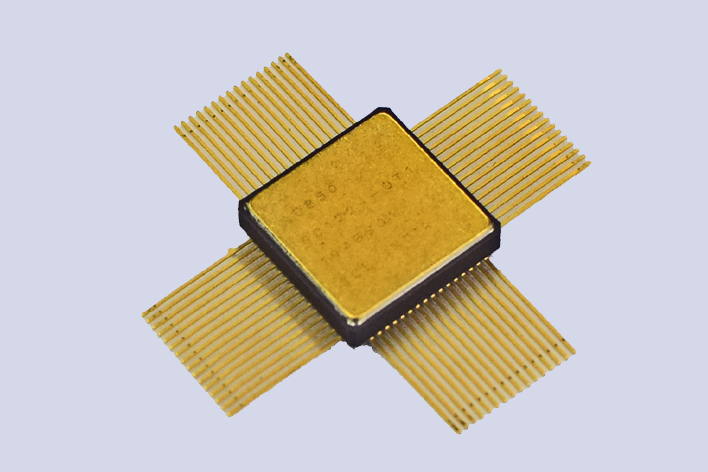

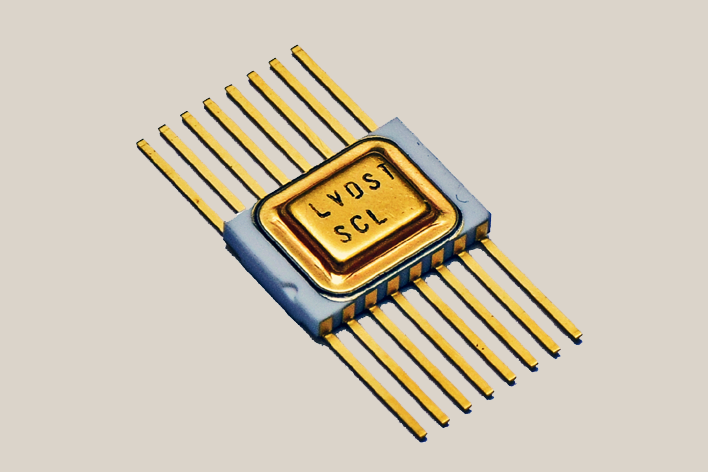

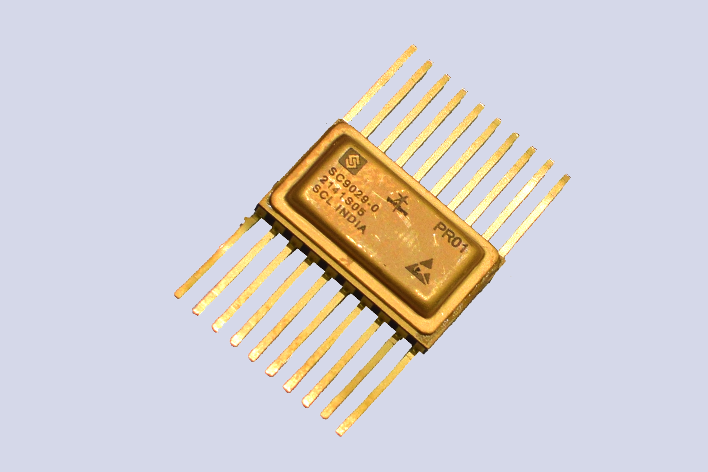

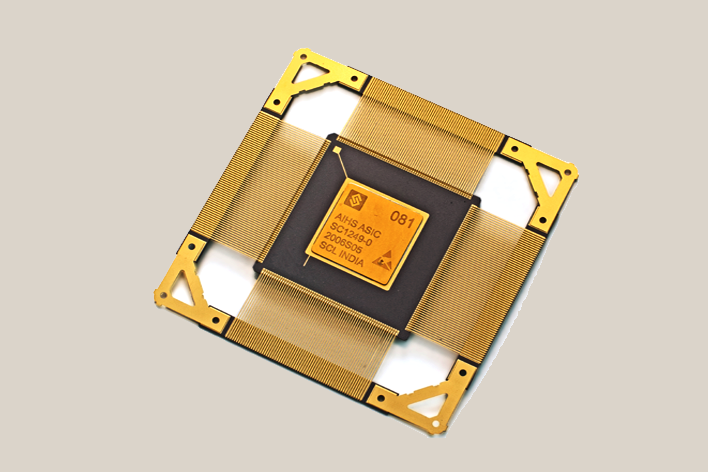

SC1203-0

Single Channel 14-Bit, 10 MSPS, CCD Analog Signal Processor with on Chip Voltage Reference

Datasheet - 1.31 MB

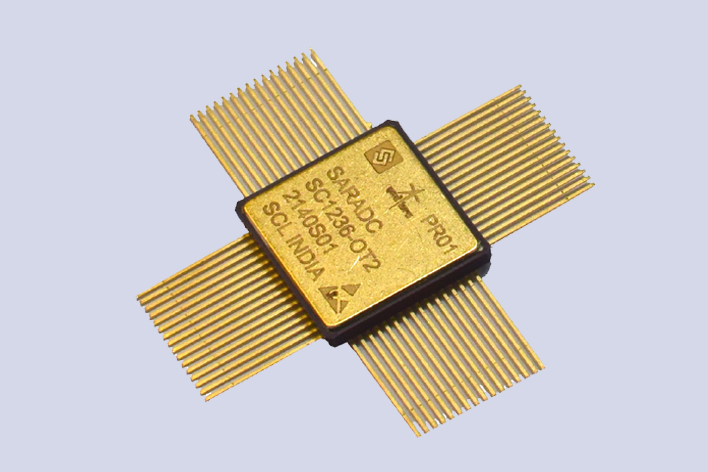

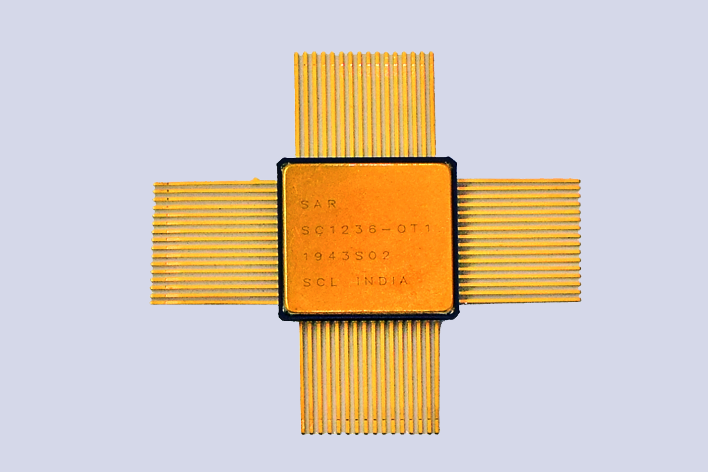

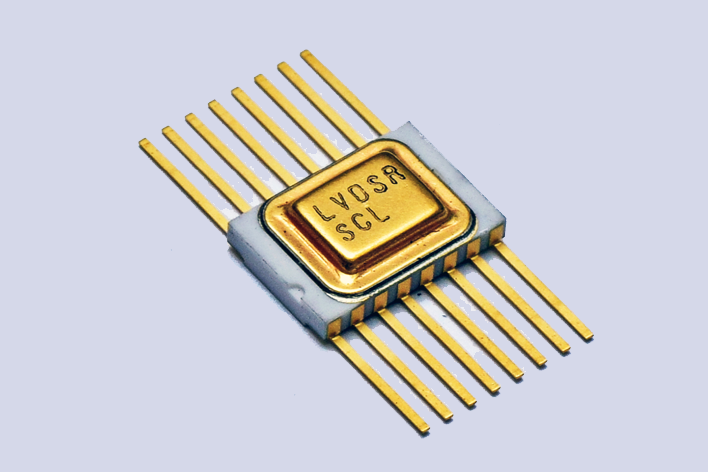

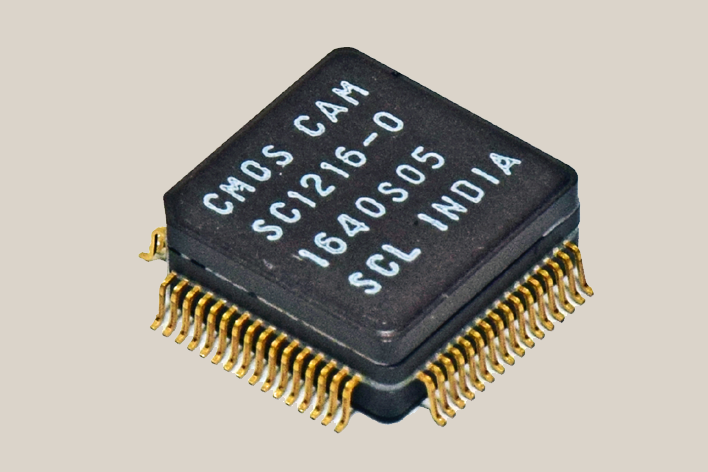

SC1261-0T1

8-Bit, 100 MSPS, Low Power Pipeline Analog To Digital Converter (ADC)

Datasheet - 1.04 MB

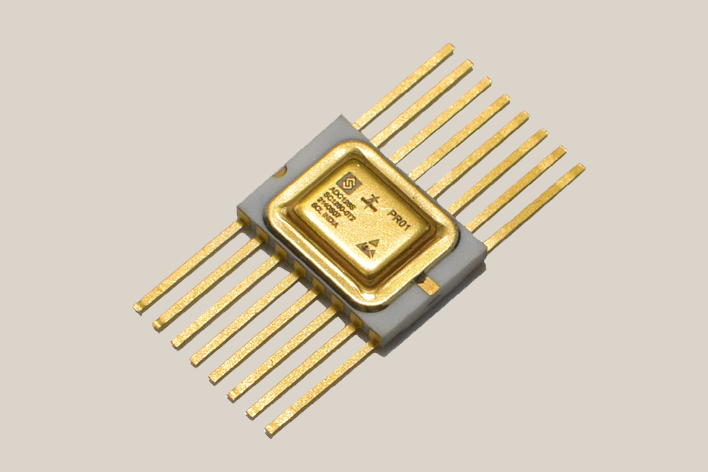

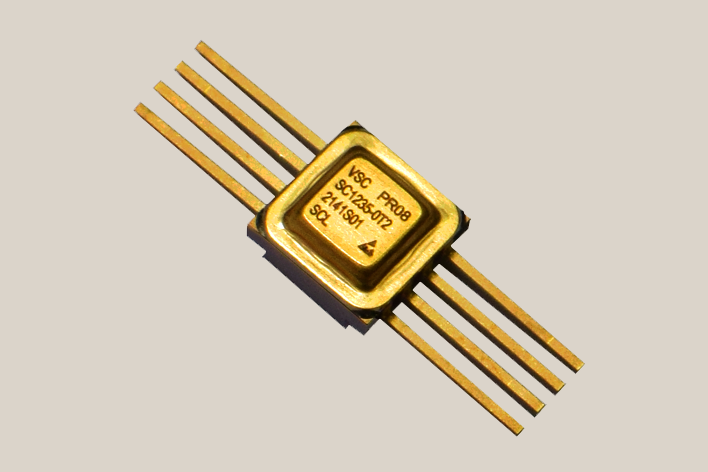

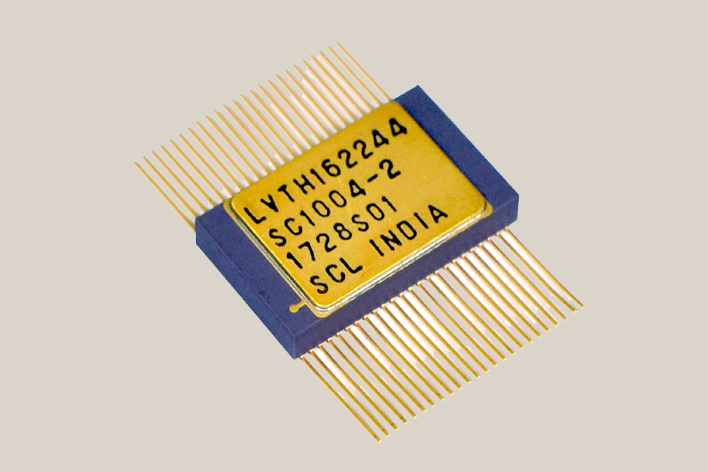

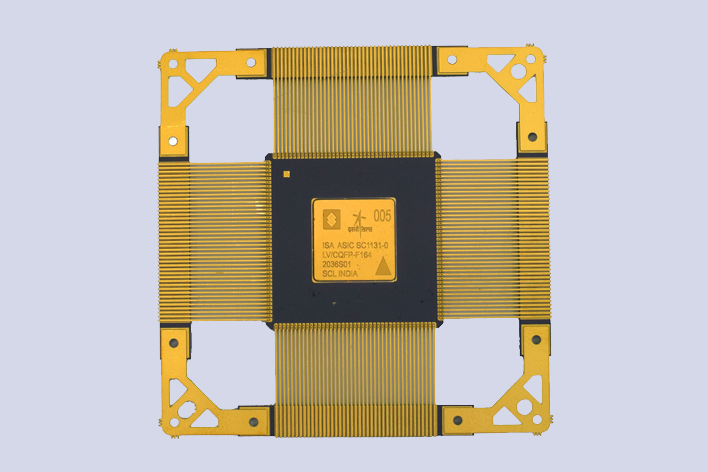

SC1004-2

16-Bit Buffer 3-State Output (Cold Sparing, Hot Insertion & 5V Tolerant Input) (Radiation Tolerant)

Datasheet - 1.55 MB

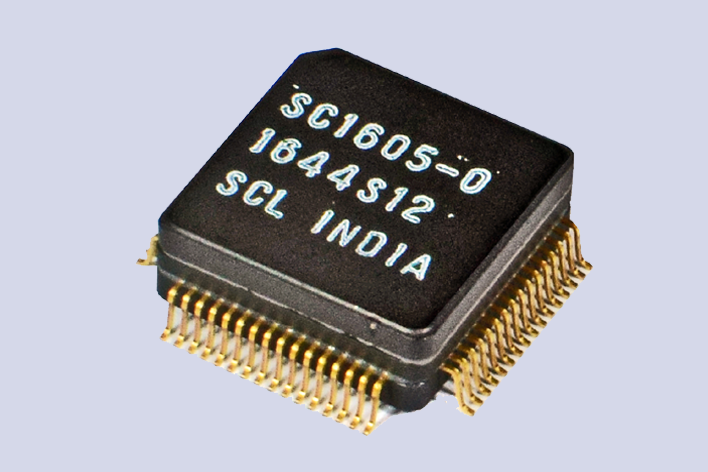

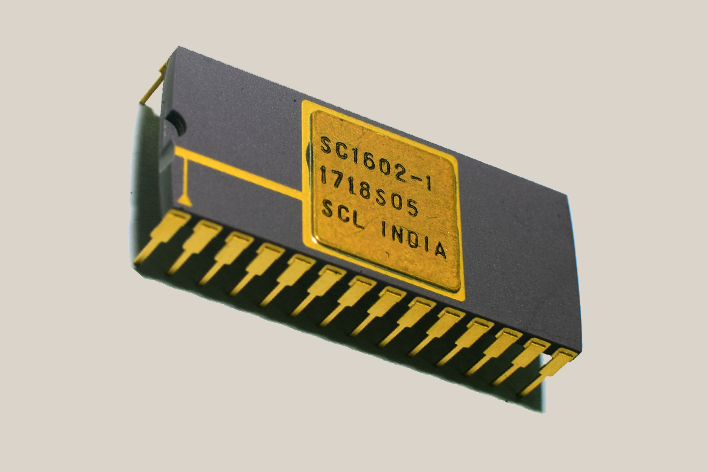

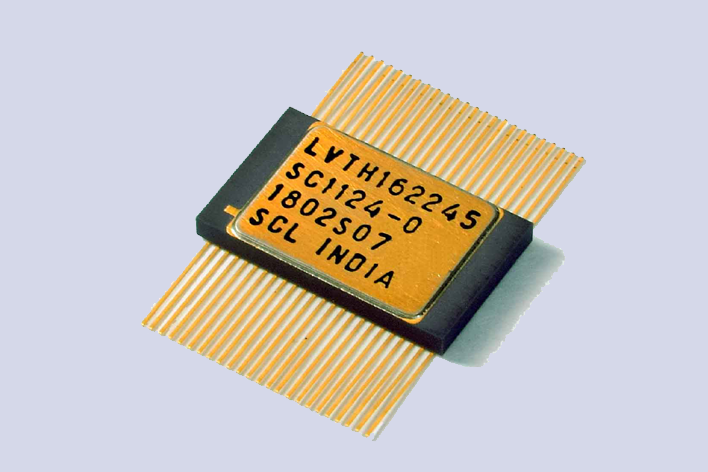

SC1124-0

16-Bit Transceiver 3-State Output (Cold Sparing, Hot Insertion & 5V Tolerant Input) (Radiation Tolerant)

Datasheet - 680 KB

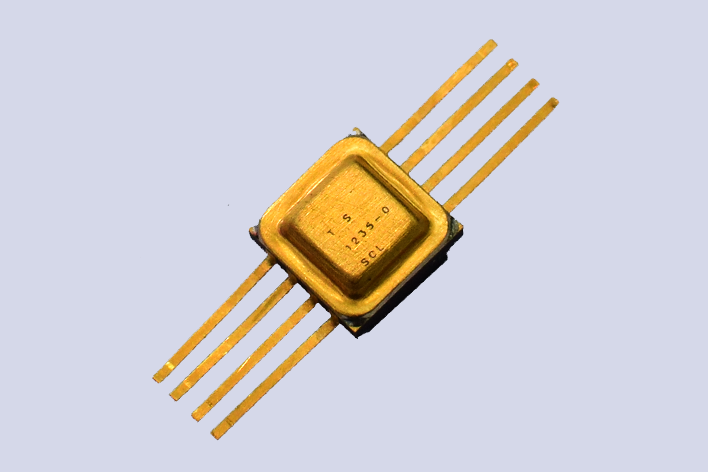

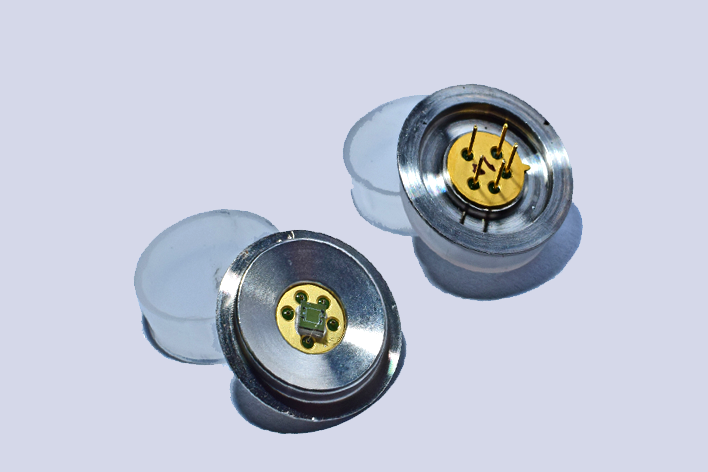

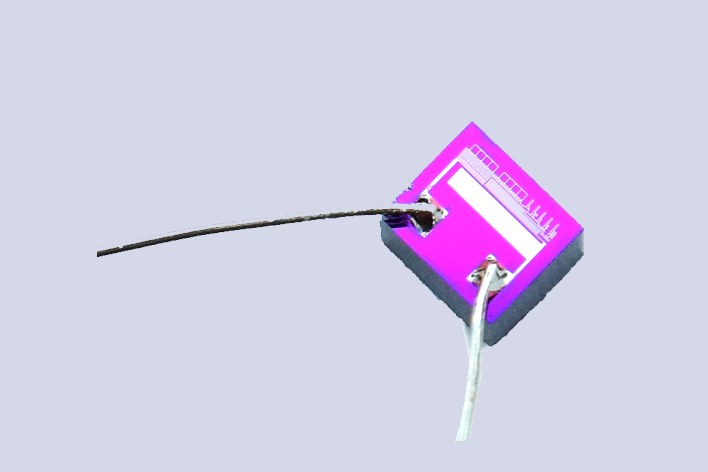

MEMS Based Pressure Sensors

Datasheet - 1.70 MB

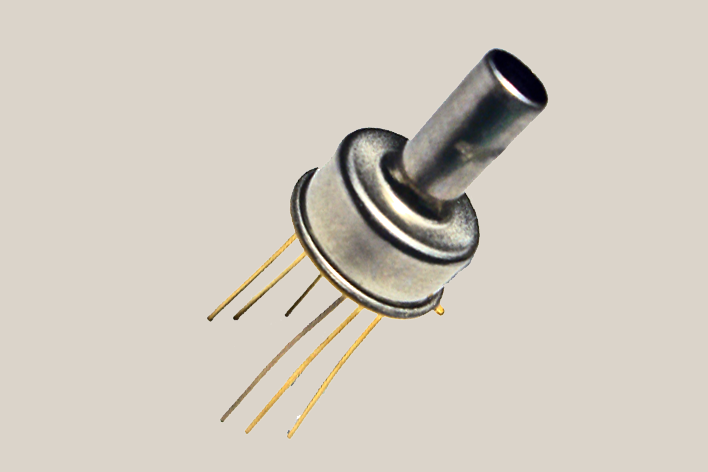

Oil Filled Pressure Sensors

Datasheet - 1.70 MB

Analog Output Smart Pressure Transducer

Datasheet - 1.71 MB

Digital Output Smart Pressure Transducer

Datasheet - 1.71 MB

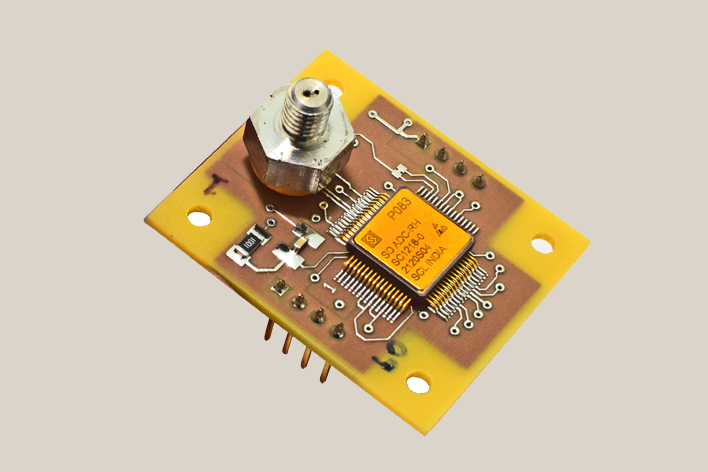

Rad Hard Digital Output (SPI) Pressure Transducer

Datasheet - 1.64 MB

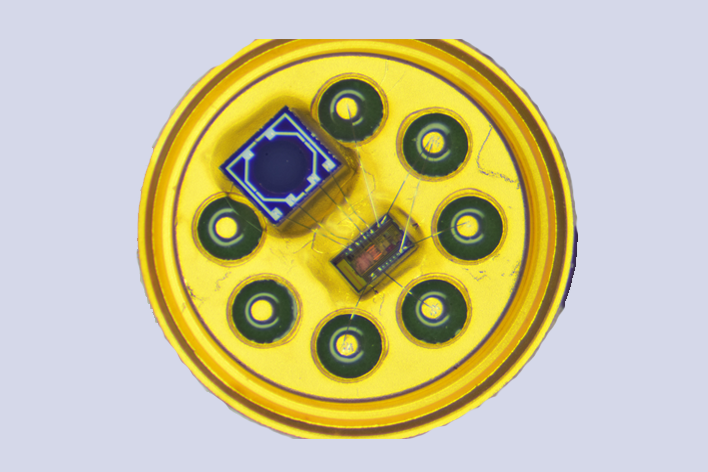

MEMS Based Accelerometer (Analog Output)

Datasheet - 1.62 MB

MEMS Based Accelerometer (Digital Output, SPI)

Datasheet - 1.71 MB

Platinum Based Temperature Sensor (PRT)

Datasheet - 1.73 MB

MEMS Based Piezo-Electric Accoustic Sensor

Datasheet - 1.81 MB