# RS422 Transceiver SC1604-0 Preliminary Datasheet

Version 1.0, April 2017

**Semi-Conductor Laboratory**

Government of India

#### PRODUCT DESCRIPTION:

RS422 (SC1604-0) is a low power differential line transceiver designed for multi-point data transmission standard RS422 applications. The CMOS design offers significant power saving over its bipolar counterpart without sacrificing ruggedness against ESD damage. It offers a choice of active-high or active-low inputs. The device is designed for line/bus transmission at switching rates up to 5 MHz

#### **FEATURES:**

- Operates From Single 3.3V  $V_{CC}$

- Switching Rates up to 5 MHz

- Transmission Rate to 10 Mbps

- Designed for RS422 applications

- Fail safe feature guarantees high output state when receiver inputs are left open.

- Common Mode Output Voltage Range: 0V to 3V

#### **DEVICE SUMMARY:**

| Silicon No. | Package | Pins | Lead Finish | Description          | Temp. range    |

|-------------|---------|------|-------------|----------------------|----------------|

| SC1604-0    | DIP     | 16   | Gold        | RS422<br>Transceiver | -40 to +125 °C |

Table 1: Device Summary

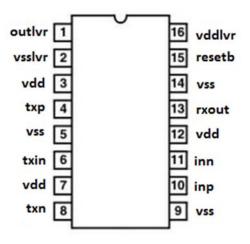

#### **PIN CONFIGURATION:**

Figure-1: Device Pin diagram

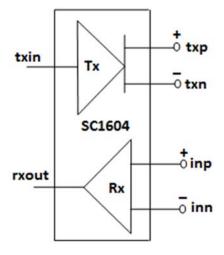

#### LOGIC DIAGRAM:

Figure-2: Device Logic Diagram

## PIN DESCRIPTION:

| SYMBOL       | PIN        | PIN DESCRIPTION            |

|--------------|------------|----------------------------|

| vdd          | 3,7,12     | Supply Voltage (3.3V)      |

| vddlvr       | 16         | 3.3V supply of LVR         |

| resetb       | 15         | Active low regulator reset |

| txin         | 6          | Driver input               |

| txp, txn     | 4, 8       | Driver outputs             |

| rxout        | 13         | Receiver output            |

| outlvr       | 1          | Output of LVR              |

| Inp, inn     | 10, 11     | Receiver inputs            |

| vss & vsslvr | 5,9,14 & 2 | Ground (0V)                |

Table-2: Device Pin description

# **FUNCTIONAL TABLE:**

| Dri   | ver    |   | Receiver |        |   |  |

|-------|--------|---|----------|--------|---|--|

| Input | Output |   | Inp      | Output |   |  |

| 1     | Н      | L | 1        | 0      | Н |  |

| 0     | L      | Н | 0        | 1      | L |  |

Table 3: Truth table

# BASIC DC-PARAMETER TESTING & TEST CONDITIONS:

| Test name      | Test Parameter      | Pins Tested                | Force                  | Min      | Typ.    | Max      | Unit |

|----------------|---------------------|----------------------------|------------------------|----------|---------|----------|------|

| ESD Diode      | Positive Diode      | All Input /                | 100uA                  | 416.175  |         | 541.205  | mV   |

| Test           | Negative Diode      | All Input /<br>Output Pins | -100uA                 | -569.982 |         | -479.224 |      |

| Static supply  | $ m I_{DD}$         | All inputs Low             | VDD = 3.3V<br>VIL=0V   |          | 944.074 |          | nA   |

| current        |                     | All Inputs High            | VDD = 3.3V<br>VIH=3.3V |          | 944.074 |          |      |

| Static supply  | I <sub>DD LVR</sub> | All inputs Low             | VDD = 3.3V<br>VIL=0V   | 4.541    |         | 4.749    | mA   |

| current of LVR |                     | All Inputs High            | VDD = 3.3V<br>VIH=3.3V | 4.541    |         | 4.673    |      |

<sup>\*0.1</sup>uF Capacitor must be between connected lyrout and vsslyr Pins.

|                            | IIL                 | Inputs (txin, Resetb)         | $V_{IN} = 0V$   | -0.170  | -0.063  |     |

|----------------------------|---------------------|-------------------------------|-----------------|---------|---------|-----|

| Input Gate<br>Leakage Test | IIH                 |                               | $V_{IN} = 3.3V$ | -0.039  | 0.016   | μΑ  |

| (VDD = 3.3V)               | IIL                 | Inputs (inn, inp)             | $V_{IN} = 0V$   | -7.071  | -2.924  |     |

|                            | IIH                 |                               | $V_{IN} = 3.3V$ | 2.391   | 7.561   |     |

| V                          | Outset Valtaga I am | Load = 0.1mA                  |                 | 0.698   | 21.973  | μA  |

| $V_{ m OL}$                | Output Voltage Low  | Load = 20mA                   |                 | 275.808 | 311.104 | m v |

| V                          | Output Voltage High | Load = -0.1 mA                |                 | 3.205   | 3.287   | V   |

| $V_{\mathrm{OH}}$          | Output Voltage High | tput Voltage High Load =-20mA |                 | 2.860   | 2.890   | V   |

# DRIVER ELECTRICAL AND SWITCHING CHARACTERISTICS

| Symbol                 | Parameter                                                  | Test Condition                                                                                                                                   |                     | Min | Typical    | Max      | Unit |

|------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|------------|----------|------|

|                        |                                                            | $R_L = 100 \Omega$                                                                                                                               | Driver Input = 0V   |     | -2.537     |          | -    |

| Vod (SS)               | Steady-State differential                                  | Refer Figure 3                                                                                                                                   | Driver Input = 3.3V |     | 2.547      |          |      |

| [ ¥ OD (SS)]           | output voltage                                             | $V_{CM} = 0V \text{ to } 3V$                                                                                                                     | Driver Input = 0V   |     | -2.032     |          |      |

|                        |                                                            | Refer Figure 4                                                                                                                                   | Driver Input = 3V   |     | 2.049      |          | V    |

| AlVan gal              | Change in magnitude of Steady-State differential           | $R_L = 100 \Omega$                                                                                                                               | Driver Input = 0V   |     | 0.010      |          |      |

| $\Delta  V_{OD (SS)} $ | output voltage between states                              | Refer Figure 3                                                                                                                                   | Driver Input = 3.3V |     | 0.017      |          |      |

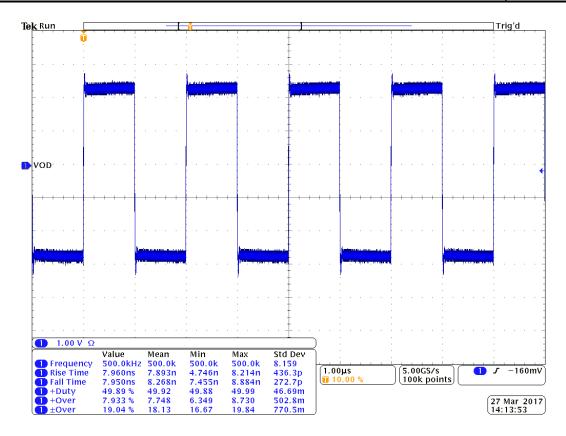

| <b>1</b> 7             | Differential output<br>voltage overshoot and<br>undershoot | $\begin{aligned} R_L &= 100~\Omega \\ C_L &= 50~pF \\ \text{Input PRR=500KHz,} \\ \text{50\% Duty Cycle} \\ \text{Refer Figure 6} \end{aligned}$ | Positive Overshoot  |     | 7.933      |          | %    |

| Vod (RING)             |                                                            |                                                                                                                                                  | Negative Overshoot  |     | 19.04      | <i>y</i> | 70   |

| V <sub>OC (PP)</sub>   | Peak-to-peak common-                                       | -                                                                                                                                                |                     |     | To be      |          |      |

| 7 00 (11)              | mode output voltage                                        |                                                                                                                                                  |                     |     | done       |          |      |

| Voc (SS)               | Steady-state common-<br>mode output voltage                |                                                                                                                                                  | -                   |     | To be done |          |      |

| Idd (D)                | Dynamic Current Supply Test                                | $V_{DD} = 3.3V$<br>Input Pulse Rate = 5 MHz                                                                                                      |                     |     | 4.9        |          | mA   |

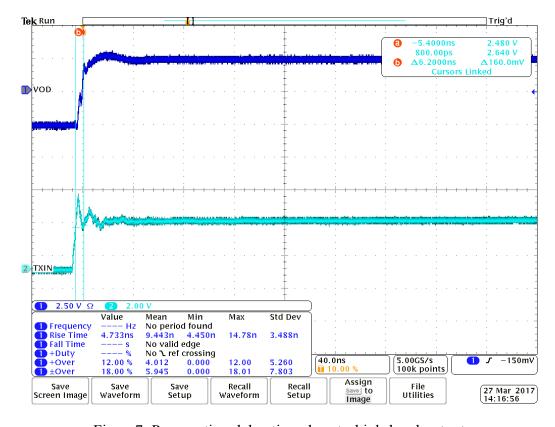

| t <sub>PLH</sub>       | Propagation delay time, low-to-high-level output           |                                                                                                                                                  | = 100 Ω             |     | 6.2        |          | ns   |

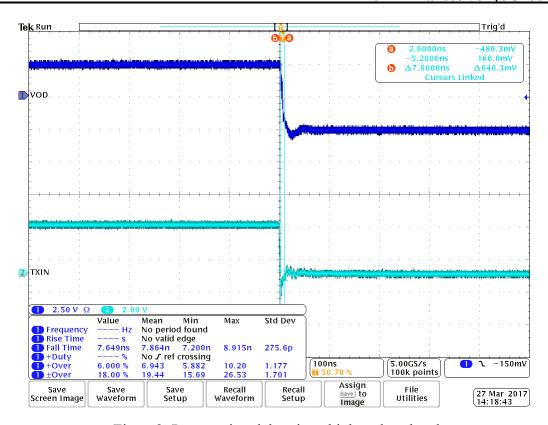

| $t_{ m PHL}$           | Propagation delay time, high-to-low-level output           | $C_L = 50 \text{ pF}$                                                                                                                            |                     |     | 7.8        |          | 115  |

| RECEIVER | FLECTRICAL | AND SWITCHING | CHARACTERISTICS |

|----------|------------|---------------|-----------------|

|          |            |               |                 |

| Parameter                   | Test Condition                              | Min | Typical | Max | Unit |

|-----------------------------|---------------------------------------------|-----|---------|-----|------|

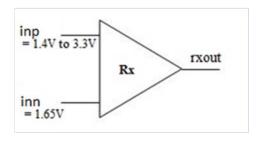

| Input Sensitivity           | $V_{CM}=0$ to $3V$                          | 50  | 200     |     | mV   |

| Input Hysteresis            | V <sub>CM</sub> = 1.65V, Refer Figure 9     |     | 43      |     | mV   |

| Dynamic Current Supply Test | $V_{DD} = 3.3V$<br>Input Pulse Rate = 5 MHz |     | 4.8     |     | mA   |

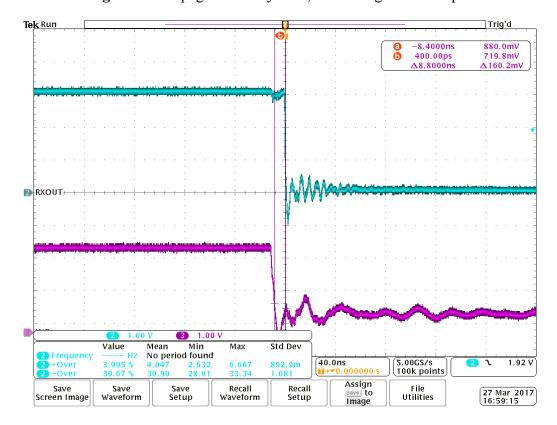

| tplн                        | Propagation Delay                           |     | 10.8    |     | ns   |

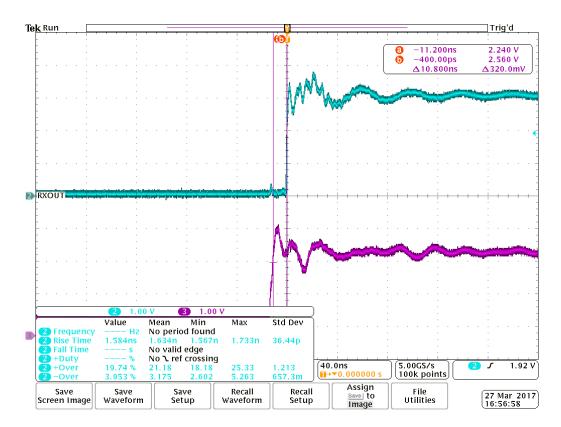

| t <sub>PHL</sub>            | Refer Figure 10                             |     | 8.8     |     | ns   |

| Duty Cycle                  |                                             |     | 49.88   |     | %    |

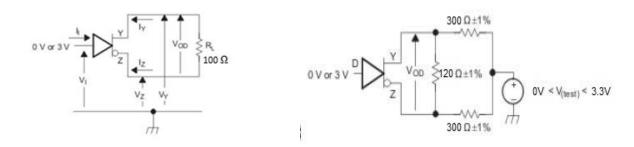

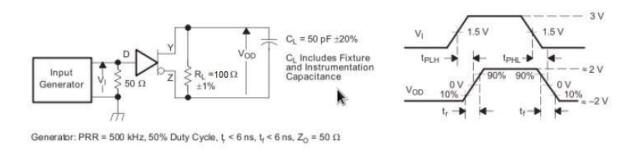

# **DRIVER TEST CIRCUITS AND WAVEFORMS:**

Figure 3: Driver VOD Test Circuit Figure 4: Driver VOC Test Circuit

Figure 5: Driver Propagation Delay Test Circuit and Waveforms

Figure6: The Driver VOD (Ring) Test Waveform

Figure 7: Propagation delay time, low-to-high-level output

Figure8: Propagation delay time, high-to-low-level output

## RECEIVER TEST CIRCUIT AND WAVEFORM:

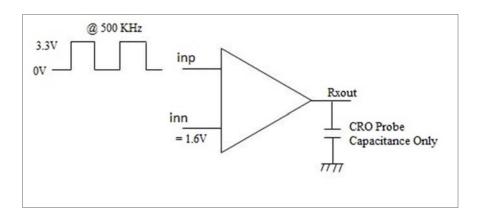

Figure9: Receiver Input Hysteresis Test Circuit

Figure 10: Receiver Propagation Delay Test Circuit

Figure 11: Propagation delay time, low-to-high-level output

Figure 12: Propagation delay time, high-to-low-level output