# FRAME TRANSFER CCD IMAGER

# 4K X 48 - OCM3

(SD3101-0)

DATASHEET

Version 1.0, Aug 2017

Semi–Conductor Laboratory Government of India S.A.S. Nagar, Punjab-160071 www.scl.gov.in

## **FEATURES**

- 10μm × 10μm pixel size

- 10µm pixel pitch

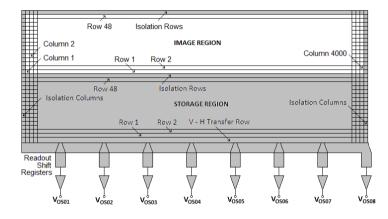

- 4000 columns × 48 rows Image and Storage regions

- Eight output ports with cascading feature for reduced number of outputs

#### **Device Description**:

The SD3101-0 is a Frame Transfer imager with 10 $\mu$ m square pixels with 4000 × 48 element Image and Storage regions. There are eight outputs with cascading feature whereby fewer outputs may be employed for readout by cascading signal from one shift register to the next, bypassing an

output. The imager is designed for off-chip TDI mode and employs metal straps across the image region for feeding clock signals. This affects photo response uniformity in frame transfer imaging snap-shot mode.

The parallel shift registers are of 4-phase N-buried channel type, serving the multiple purposes of photo-detection, charge integration and charge transfer. The read-out shift registers, like the parallel shift registers, are of 4-phase N-buried channel type. The signal from 500 photo-sensitive elements associated with each read-out shift register is read out of the corresponding output. Signal charge from multiple (2, 4 or 8) read-out shift registers may be read out through a single output by employing the cascading feature, which is done by applying appropriate clock signals. This reduces the number of outputs. For the case of cascading of 2 shift registers to one output, all the unused outputs may be powered off.

Each output section comprises a floating diffusion charge detection node, a reset transistor and a two-stage N-buried channel source follower amplifier.

# **Device Characteristics:**

The following table summarizes the main characteristics of the device.

| Table 1.Device Characteristics                             |                                                                                             |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| Characteristics                                            | Details                                                                                     |  |  |  |  |

| Number of photosensitive elements                          | $4000 \times 48$                                                                            |  |  |  |  |

| Pixel Pitch                                                | 10µm                                                                                        |  |  |  |  |

| Pixel Size                                                 | 10μm × 10μm                                                                                 |  |  |  |  |

| Isolation rows                                             | 8 (between the Image and Storage regions)                                                   |  |  |  |  |

| Isolation columns                                          | 8 (At each end of array)                                                                    |  |  |  |  |

| Number of serial readout shift registers and video outputs | 8                                                                                           |  |  |  |  |

| Number of elements per read-out register (all read out)    |                                                                                             |  |  |  |  |

| Active elements                                            | 500                                                                                         |  |  |  |  |

| Pre-scan isolation elements                                | 8                                                                                           |  |  |  |  |

| Cascading option                                           | Cascading of 2, 4 or 8 outputs (giving 1000, 2000 or 4000 elements per output respectively) |  |  |  |  |

| Shift register type                                        |                                                                                             |  |  |  |  |

| - Parallel                                                 | 4-Phase N buried channel                                                                    |  |  |  |  |

| - Serial                                                   | 4-Phase N buried channel                                                                    |  |  |  |  |

| Charge detection node                                      | Floating diffusion type                                                                     |  |  |  |  |

| Output amplifier                                           | 2-stage buried channel source follower type                                                 |  |  |  |  |

# **Pin Descriptions:**

The following table lists the device pins grouped according to their functions.

| Tabl         | Table 2.   Pin Descriptions                            |     |  |  |  |  |  |

|--------------|--------------------------------------------------------|-----|--|--|--|--|--|

| Pin          | Pin description                                        | Pin |  |  |  |  |  |

|              |                                                        | No. |  |  |  |  |  |

| VOFG         | Overflow gate bias                                     | 38  |  |  |  |  |  |

| VOFD         | Overflow drain bias                                    | 57  |  |  |  |  |  |

| ΦΙ1          | Image zone shift register transport clocks (Phase 1)   | 40  |  |  |  |  |  |

| ΦΙ2          | Image zone shift register transport clocks (Phase 2)   | 41  |  |  |  |  |  |

| ΦΙ3          | Image zone shift register transport clocks (Phase 3)   | 43  |  |  |  |  |  |

| ΦΙ4          | Image zone shift register transport clocks (Phase 4)   | 44  |  |  |  |  |  |

| Φ <b>S</b> 1 | Storage zone shift register transport clocks (Phase 1) | 55  |  |  |  |  |  |

| Φ <b>S</b> 2 | Storage zone shift register transport clocks (Phase 2) | 54  |  |  |  |  |  |

| ΦS3          | Storage zone shift register transport clocks (Phase 3) | 52  |  |  |  |  |  |

| ΦS4          | Storage zone shift register transport clocks (Phase 4) | 51  |  |  |  |  |  |

| ΦVΗ          | Parallel to serial register transfer clock             | 59  |  |  |  |  |  |

| ФН1          | Serial readout register transport clock (Phase 1)      | 2   |  |  |  |  |  |

| ΦH2          | Serial readout register transport clock (Phase 2)      | 5   |  |  |  |  |  |

## FRAME TRANSFER CCD IMAGER 4K X 48 - OCM3 (SD3101-0)

| Pin          | Pin description                                                               | Pin<br>No. |

|--------------|-------------------------------------------------------------------------------|------------|

| ФН3          | Serial readout register transport clock (Phase 3)                             | 3          |

| ΦH4          | Serial readout register transport clock (Phase 4)                             | 6          |

| ΦHC1         | Serial readout register cascade clock for cascading 2 registers. (Clocked to  | 7          |

| THE          | bypass SR 1, 3, 5 & 7)                                                        | ,          |

| ΦHC2         | Serial readout register cascade clock for cascading 4 registers. (Clocked to  | 8          |

|              | bypass SR 2 & 6)                                                              |            |

| ΦHC3         | Serial readout register cascade clock for cascading 8 registers. (Clocked to  | 9          |

|              | bypass SR 4)                                                                  |            |

| $\Phi$ HT1   | Serial readout register tap clock for cascading 2 registers. (Clocked to read | 26         |

|              | out SR 1, 3, 5 & 7)                                                           |            |

| $\Phi$ HT2   | Serial readout register tap clock for cascading 4 registers. (Clocked to read | 27         |

|              | out SR 2 & 6)                                                                 |            |

| ΦHT3         | Serial readout register tap clock for cascading 8 registers. (Clocked to read | 28         |

|              | out SR 8)                                                                     |            |

| Φ <b>R1</b>  | Reset clock for outputs 1, 3, 5 and 7                                         | 31         |

| ΦR2          | Reset clock for outputs 2, 4, 6 and 8                                         | 30         |

| VOG          | Output gate DC bias                                                           | 34         |

| VRD1         | Reset drain supply for outputs 1, 3, 5 and 7                                  | 49         |

| VRD2         | Reset drain supply for outputs 2, 4, 6 and 8                                  | 46         |

| VDD1         | Output amplifier drain supply for outputs 1, 3, 5 and 7                       | 47         |

| VDD2         | Output amplifier drain supply for outputs 2, 4, 6 and 8                       | 48         |

| VOS1         | Video output 1                                                                | 10         |

| VOS2         | Video output 2                                                                | 12         |

| VOS3         | Video output 3                                                                | 14         |

| VOS4         | Video output 4                                                                | 16         |

| VOS5         | Video output 5                                                                | 18         |

| VOS6         | Video output 6                                                                | 20         |

| VOS7         | Video output 7                                                                | 22         |

| VOS8         | Video output 8                                                                | 24         |

| VS1          | Amplifier signal ground 1                                                     | 11         |

| VS2          | Amplifier signal ground 2                                                     | 13         |

| VS3          | Amplifier signal ground 3                                                     | 15         |

| VS4          | Amplifier signal ground 4                                                     | 17         |

| VS5<br>VS6   | Amplifier signal ground 5                                                     | 19         |

| V36<br>VS7   | Amplifier signal ground 6<br>Amplifier signal ground 7                        | 21         |

|              |                                                                               | 23         |

| VS8<br>VTS1  | Amplifier signal ground 8<br>Temperature Sensor 1                             | 25<br>63   |

| VTS1<br>VTS2 | Temperature Sensor 1<br>Temperature Sensor 2                                  | 36         |

| VISZ         | Heating Element                                                               | 36<br>60   |

| VPD          | Protection Drain                                                              | 62         |

| VPD          | Substrate contact / Light Shield                                              | 1          |

| VSS          |                                                                               | 4          |

| 222          | Substrate contact / Light Shield                                              | 4          |

# FRAME TRANSFER CCD IMAGER 4K X 48 - OCM3 (SD3101-0)

| Pin | Pin description                  | Pin |

|-----|----------------------------------|-----|

|     |                                  | No. |

| VSS | Substrate contact / Light Shield | 29  |

| VSS | Substrate contact / Light Shield | 32  |

| VSS | Substrate contact / Light Shield | 33  |

| VSS | Substrate contact / Light Shield | 35  |

| VSS | Substrate contact / Light Shield | 37  |

| VSS | Substrate contact / Light Shield | 39  |

| VSS | Substrate contact / Light Shield | 42  |

| VSS | Substrate contact / Light Shield | 45  |

| VSS | Substrate contact / Light Shield | 50  |

| VSS | Substrate contact / Light Shield | 53  |

| VSS | Substrate contact / Light Shield | 56  |

| VSS | Substrate contact / Light Shield | 58  |

| VSS | Substrate contact / Light Shield | 61  |

| VSS | Substrate contact / Light Shield | 64  |

# **Device Operating Conditions:**

#### Table 3.DC Operating Conditions:

| Bias Names                      | Pin                               | Number of   | value (v) |         | Max | Number of          | Remarks   |                                                                           |

|---------------------------------|-----------------------------------|-------------|-----------|---------|-----|--------------------|-----------|---------------------------------------------------------------------------|

|                                 | Symbol(s)                         | device pins | Min       | Typical | Max | current per<br>pin | bond pads |                                                                           |

| Overflow Drain Bias             | V <sub>OFD</sub>                  | 1           | 12        | 13      | 14  | 1nA                | 1         |                                                                           |

| Overflow Gate Bias              | V <sub>OFG</sub>                  | 1           | 0.5       | 1       | 2   | 1nA                | 1         |                                                                           |

| Output Gate Bias                | V <sub>OG</sub>                   | 1           | 0.5       | 1       | 2   | 1nA                | 1         |                                                                           |

| Protection Drain Bias           | $V_{PD}$                          | 1           | 12        | 13      | 14  | 1nA                | 1         |                                                                           |

| Reset Drain Bias                | V <sub>DR1</sub>                  | 1           | 12        | 13      | 14  | 1 1 ۸              | 4         |                                                                           |

| Reset Dialii Dias               | V <sub>DR2</sub>                  | 1           | 12        | 15      | 14  | 1.1µA              | 4         |                                                                           |

| Output Amplifier                | $V_{DD1}$                         | 1           | 17        | 18      | 19  | 30mA               | 4         |                                                                           |

| Drain Bias                      | $V_{DD2}$                         | 1           | 1/        | 10      | 19  | JUIIA              | 4         |                                                                           |

| Output Amplifier<br>Source Bias | V <sub>S1</sub> - V <sub>S8</sub> | 8           | 0         | 0       | 0.1 | -8mA               | 8         | The eight $V_s$ pins are the return paths for the eight output terminals. |

| Heat Dissipation Bias           | $V_{HD}$                          | 1           |           |         |     |                    | 1         | The operating conditions of the heat dissipator                           |

| Tomporatura Concor              | V <sub>TS1</sub>                  | 1           |           |         |     |                    | 1         | and the temperature sensors are to be finalised                           |

| Temperature Sensor              | V <sub>TS2</sub>                  | 1           |           |         |     |                    | 1         | after devices are characterised.                                          |

| Substrate Bias                  | V <sub>SS</sub>                   | TBD         | -0.1      | 0       | 0   |                    | 12        | These are the contacts to the P-type substrate.                           |

Note: The currents specified are for each pin. The current is divided equally among the multiple pads if there. For example, the two V<sub>DD</sub> pins will draw a maximum of 30mA each, which is again the sum of 7.5mA per bond pad.

## Table 4.AC Operating Conditions:

| Clock Names                               | Pin Symbol          | Number of   | Low | Level | High | Level | Rise | Fall | Capacitance | Number of |

|-------------------------------------------|---------------------|-------------|-----|-------|------|-------|------|------|-------------|-----------|

|                                           |                     |             | Min | Max   | Min  | Max   | Time | Time | (per pin)   | bond pads |

|                                           |                     | device pins | V   | V     | V    | V     | ns   | ns   | pF          |           |

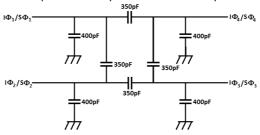

| Image Zone Shift<br>Register Clocks       | $I\Phi 1 - I\Phi 4$ | 4           | 0.4 | 0.6   | 11   | 13    | 200  | 200  | 3000        | 4         |

| Storage Zone Shift<br>Register Clocks     | $S\Phi1-S\Phi4$     | 4           | 0.4 | 0.6   | 11   | 13    | 200  | 200  | 3000        | 4         |

| Parallel to Serial<br>Transfer Clock      | $\Phi_{ m VH}$      | 1           | 0.4 | 0.6   | 11   | 13    | 200  | 200  | 150         | 1         |

|                                           | ΗΦ1                 | 1           |     |       |      |       |      |      |             | 8         |

| Serial Register                           | ΗΦ2                 | 1           | 0.4 | 0.6   | 11   | 13    | 10   | 10   | 150         | 9         |

| Transport Clocks                          | ΗΦ3                 | 1           |     |       |      |       |      |      |             | 9         |

|                                           | ΗΦ4                 | 1           |     |       |      |       |      |      |             | 8         |

| Carial Davistan Tan                       | ΗΦΤ1, ΗΦC1          | 1 + 1       |     |       |      |       |      |      |             | 4         |

| Serial Register Tap<br>and Cascade Clocks | ΗΦΤ2, ΗΦC2          | 1 + 1       | 0.4 | 0.6   | 11   | 13    | 3 10 | 10   | 50          | 2         |

| and Cascade Clocks                        | НФТЗ, НФСЗ          | 1 + 1       |     |       |      |       |      |      |             | 1         |

| Reset Clock                               | ΦR1                 | 1           | 0.4 | 0.6   | 11   | 13    | 8    | 8    | 25          | 4         |

| Keset Clock                               | ΦR2                 | 1           | 0.4 | 0.6   | 11   |       |      |      | 25          | 4         |

Note: The capacitances specified are for each pin. For example, the fourHF pins have a capacitance load of 150pF each.

## Fig. 1. <u>Parallel shift register capacitance network</u>

Page 6 of 12

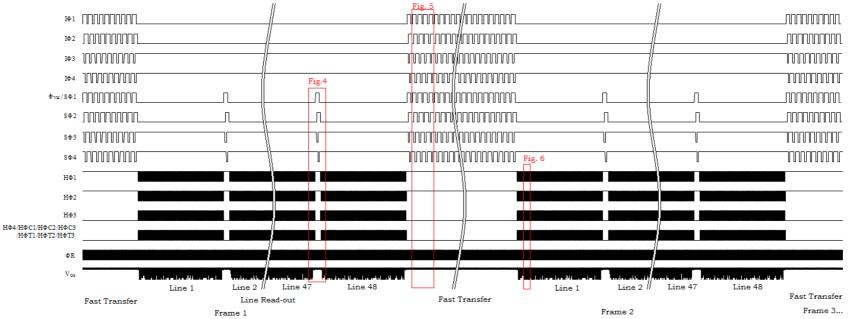

## **Clock Timing Details**

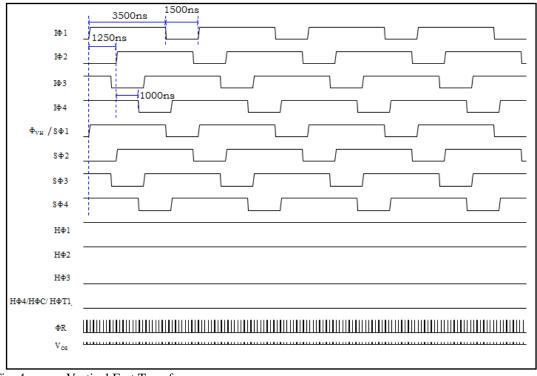

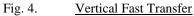

The following figures depict the tentative timing relationships between the clock signals for normal device operation. From the functional requirements, the vertical fast transfer is at 200kHz. This is shown in the figure below. The relationships between the clocks may need to be tuned after the prototype devices are obtained. Based on the device architecture and the operational requirements, the serial readout register readout rate is determined.

- Fast transfer rate: 200kHz

- Number of vertical transfers: 52

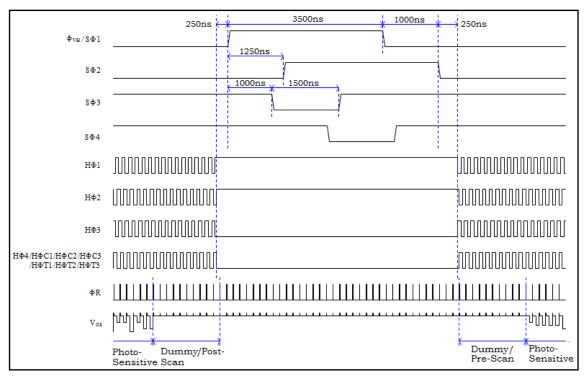

- Time gap between vertical transfer and serial readout: 250ns

- HSR elements (including pre-scan elements): 512

From the required frame rate of 220fps, the serial readout has to take place at approximately 6.67MHz.

Fig. 2. <u>Complete Frame Timing Diagram</u>

Fig. 3. Vertical Transfer and Read-out

# **Device Performance Characteristics**

The following two tables list the target electrical and electro-optical parameter values for the device. Some of these values are estimated values and may change after the fabricated devices are characterised.

The electrical parameters are to be met for 220fps and 20fps.

#### Table 5.Device Electrical Parameters

| Sr.<br>No. | Parameter                                               | Target Value                                                        | Remarks                                                                                   |

|------------|---------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 1.         | DC output level of video                                | 10V to 15V                                                          |                                                                                           |

| 2.         | DC mismatch among outputs of same device                | ≤0.5V                                                               |                                                                                           |

| 3.         | Total power dissipation at nominal readout rate         |                                                                     | Will be provided at CDR.                                                                  |

| 4.         | Video o/p drive capability                              | 220Ω to 250Ω                                                        | Final value with dispersion will be provided at CDR.                                      |

| 5.         | Leakage current                                         | ≤5nA                                                                | All gates to substrate leakage                                                            |

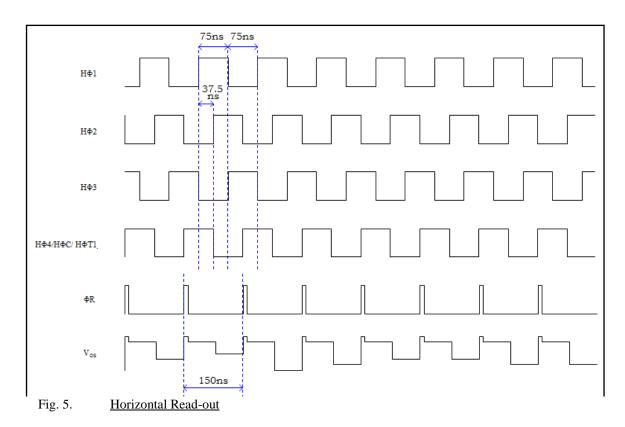

| 6.         | Reference zone / Stable zone $(\Delta T1 / \Delta T2)$  | Stable up to 10bit accuracy for $\geq 15\%$ of pixel readout range. | To be demonstrated with output<br>load capacitor value mentioned<br>in the figure 2 below |

| 7.         | Image zone to storage zone vertical transfer rate       | $\geq$ 200kHz for both frame rates                                  |                                                                                           |

| 8.         | Storage zone to horizontal shift register transfer rate | Commensurate to required frame rates                                |                                                                                           |

| 9.         | Horizontal shift register transfer rate                 | >5MHz                                                               |                                                                                           |

Fig. 6. <u>Pixel output waveform stable zones definition and output load for measuring the same.</u>

The electro-optical requirements specified below are to be met under test conditions of 20°C with frame rates of 220fps and 20fps and with F# 4.5 optics.

| Sr.<br>No. | Parameter                                   | Target V            | alue     |      |     | Remarks            |

|------------|---------------------------------------------|---------------------|----------|------|-----|--------------------|

| 1.         | Photo-site charge handling                  | ≥300ke              |          |      |     |                    |

| 2.         | capacity (Qsat)<br>Signal to noise ratio    | $\geq$ 400 at 2     | 250kg    |      |     |                    |

| 2.<br>3.   |                                             |                     | 230KC    |      |     |                    |

|            | Conversion gain                             | $>4\mu V/e$         |          |      |     |                    |

| 4.         | Readout noise                               | ≤70e                | . /      |      |     |                    |

| 5.         | Dark signal                                 | $\leq 3500 e/p$     | 0/S      |      |     |                    |

| 6.         | Dark offset                                 | $\leq 50 \text{mV}$ | 501      |      |     |                    |

| 7.         | Photo-site to light shield pixel cross-talk | $\leq 1\%$ at 2     | .50ke    |      |     |                    |

| 8.         | RMS non-linearity error (for                | ≤1%                 |          |      |     | Linearity error to |

|            | signal between 5% and 80% of                |                     |          |      |     | be demonstrated    |

|            | Qsat)                                       |                     |          |      |     | for different full |

|            |                                             |                     |          |      |     | well capacities    |

|            |                                             |                     |          |      |     | (50% and 100% of   |

| 0          | Oran tang official and and MTE              | D 1                 | <u>,</u> | OF   | MTE | Qsat)              |

| 9.         | Quantum efficiency and MTF                  | Band                | λ        | QE   | MTF |                    |

|            |                                             | D 1                 | (nm)     | (%)  | (%) | -                  |

|            |                                             | B1                  | 412      | >11  | >30 | -                  |

|            |                                             | B2                  | 443      | >11  | >30 | -                  |

|            |                                             | B3                  | 490      | >13  | >30 | -                  |

|            |                                             | B4                  | 510      | >15  | >45 | -                  |

|            |                                             | B5                  | 555      | >18  | >45 | -                  |

|            |                                             | B6                  | 566      | >16  | >45 | -                  |

|            |                                             | B7                  | 620      | >17  | >45 | -                  |

|            |                                             | B8                  | 670      | >17  | >45 | -                  |

|            |                                             | B9                  | 681      | >23  | >45 | -                  |

|            |                                             | B10                 | 710      | >18  | >30 | -                  |

|            |                                             | B11                 | 780      | >18  | >30 | -                  |

|            |                                             | B12<br>B13          | 870      | >10  | >20 | -                  |

| 10.        | Band wise average                           | D13                 | 1010     | >8.3 | >10 | To be provided     |

| 10.        | Band wise average responsivity              |                     |          |      |     | after prototype    |

|            |                                             |                     |          |      |     | devices are        |

|            |                                             |                     |          |      |     | characterised.     |

| 11.        | Pk-Pk Dark signal non-                      | ≤±5%                |          |      |     | characterisea.     |

| 11.        | uniformity                                  |                     |          |      |     |                    |

Table 6.Device electro-optical parameters

| Sr. | Parameter                      | Target Value               | Remarks              |

|-----|--------------------------------|----------------------------|----------------------|

| No. |                                |                            |                      |

| 12. | Pk-Pk band specific photo      | ≤±10%                      | For snapshot         |

|     | response non-uniformity        |                            | mode, presence of    |

|     | within pixels of an array (for |                            | metal straps will be |

|     | signal of 80% of Qsat)         |                            | considered.1         |

| 13. | Vertical transfer inefficiency | $\leq \pm 2\%$ for 80% FWC | Ok                   |

| 14. | Horizontal transfer            | For 80% FWC: ≤1%           | For 5% FWC: To       |

|     | inefficiency                   | For 5% FWC: See remarks    | be provided after    |

|     |                                |                            | prototypes are       |

|     |                                |                            | characterised.       |

| 15. | Anti-blooming operation        |                            | Not provided         |

<sup>&</sup>lt;sup>1</sup> The layout has metal straps across the photosensitive array of the device to feed clock signals to the polysilicon gates in order to meet the vertical transfer requirements. While this will reduce the effective fill factor of some pixels, it does not cause degradation of performance in actual operation because of off-chip TDI mode.