## 256Kbit CMOS (32K X 8) Static SRAM

#### **Features**

- SCL's 180nm CMOS process

- I/O Power Supply  $3.3V \pm 10\%$

- Core Power Supply  $1.8V \pm 10\%$

- Operating Temperature -55°C to 125°C

- Asynchronous 32Kx8 bits SRAM

- Fully Static operation

- High speed operation

- Access Time  $t_{AA} = 18 \text{ ns}$

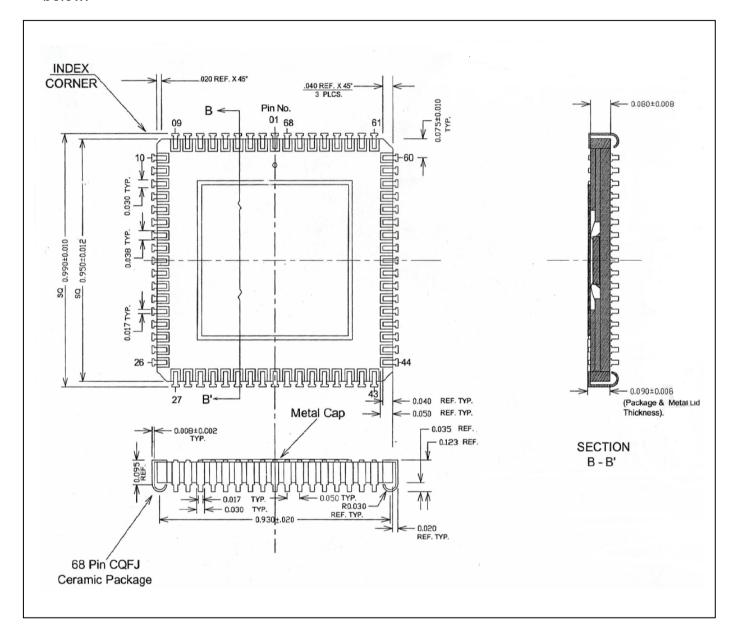

- 68 pin CQFP-J Package

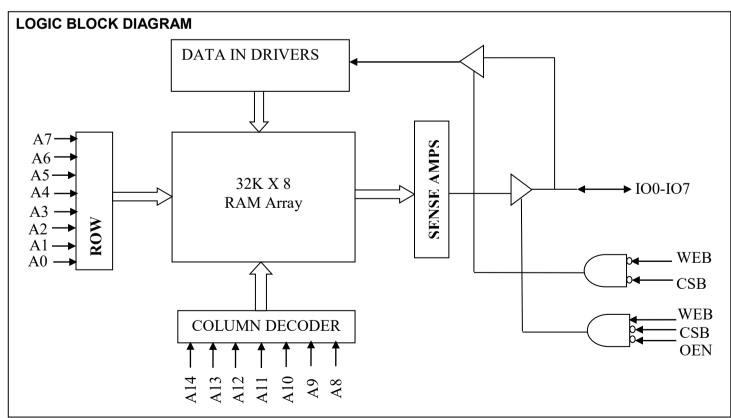

#### **Functional Description**

SC1301-1 SCL is high **CMOS RAM** performance static organized as 32,768 words by 8 bits. Writing to the device is accomplished by taking Chip Select (CSB) and Write Enable (WEB) inputs LOW. Reading from the device is accomplished by taking Chip Select (CSB) and Output Enable (OEN) LOW while forcing the Write Enable (WEB) HIGH. The complete description of Read and Write modes can be found in the truth table. The input/output pins (IO0 through IO7) are placed in a highimpedance state when the device is deselected (CSB HIGH), or OEN and WEB both are held HIGH with CSB Low.

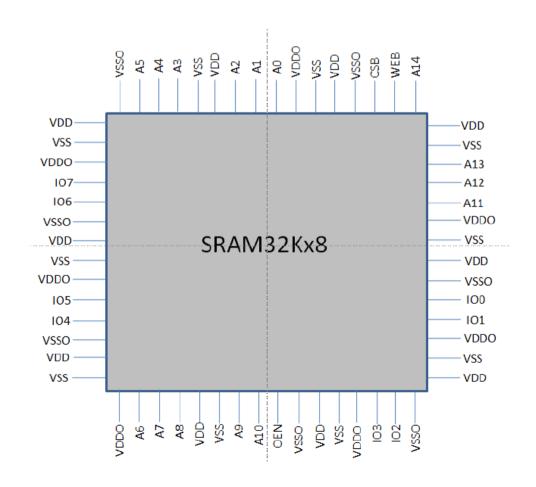

## **Pin Configurations**

| Name    | Pin Number                                  | I/O Type       | Description                         |  |

|---------|---------------------------------------------|----------------|-------------------------------------|--|

| A0-A14  | 68,1,2,5,6,7,28,29,30,<br>33,34,55,56,57,61 | Input          | Address inputs<br>(A14 as MSB)      |  |

| 100-107 | 49,48,41,40,22,21,15,<br>14                 | Input / Output | Data Input / Output<br>(IO7 as MSB) |  |

| CSB     | 63                                          | Input          | Chip Select (Active low)            |  |

| WEB     | 62                                          | Input          | Write Enable<br>(Active low)        |  |

| OEN     | 35                                          | Input          | Output Enable (Active low)          |  |

| VDDO    | 13,20,27,39,47,54,67                        | Power Supply   | I/O supply (3.3 V)                  |  |

| VDD     | 3,11,17,24,31,37,45,<br>51,59,65            | Power Supply   | Core Supply (1.8 V)                 |  |

| VSSO    | 8,16,23,36,42,50,64                         | Ground         | I/O Ground                          |  |

| VSS     | 4,12,19,25,32,38,46,<br>53,58,66            | Ground         | Core Ground                         |  |

# **Absolute Maximum Ratings**

| Symbol    | Rating                                          | Value  |  |

|-----------|-------------------------------------------------|--------|--|

| $V_{DDO}$ | IO supply Voltage relative to Vsso              | 4.3 V  |  |

| $V_{DD}$  | Core supply Voltage relative to V <sub>SS</sub> | 2.2 V  |  |

| TJ        | Operating Temperature (Junction)                | 125 °C |  |

### **Truth Table**

| WEB | CSB | OEN | Ю      | Function       |

|-----|-----|-----|--------|----------------|

| Х   | Н   | Х   | High-Z | Disabled       |

| Н   | L   | Н   | High-Z | Output Disable |

| Н   | L   | L   | Dout   | Read           |

| L   | L   | Х   | Din    | Write          |

# **DC Electrical Characteristics over the Operating Range**

| Parameter                               | Conditions                                                       | Symbol              | Typical<br>Value | Unit |

|-----------------------------------------|------------------------------------------------------------------|---------------------|------------------|------|

| Dynamic<br>Operating Current            | CSB <vil v<sub="">DD=max,</vil>                                  | l <sub>DD</sub>     | 134              | mA   |

|                                         | f=f <sub>MAX</sub>                                               | I <sub>DDO</sub>    | 23               | mA   |

| Standby Power<br>Supply Current         | CSB=V <sub>IH</sub> V <sub>DD</sub> =max,                        | IDDSB               | 1.8              | mA   |

|                                         | f=f <sub>MAX</sub>                                               | IDDOSB              | 8                | mA   |

| Full Standby<br>Power Supply<br>Current | CSB=V <sub>IH</sub> V <sub>DD</sub> =max,<br>f=0                 | I <sub>DDSB1</sub>  | 1                | μΑ   |

|                                         |                                                                  | I <sub>DDOSB1</sub> | 28               | μΑ   |

| Input Leakage<br>Current                | V <sub>DD</sub> =max,<br>V <sub>IN</sub> =GND or V <sub>DD</sub> | lıL/lıн             | 100              | nA   |

| Output Low<br>Voltage                   | $V_{DDO}$ =min; $I_{OL} = -8$ mA                                 | V <sub>OL</sub>     | 115.15           | mV   |

| Output High<br>Voltage                  | $V_{DDO}$ =min;<br>$I_{OH} = +8mA$                               | Vон                 | 3.12             | mV   |

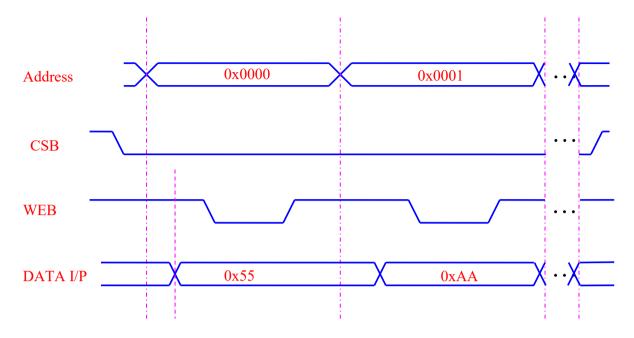

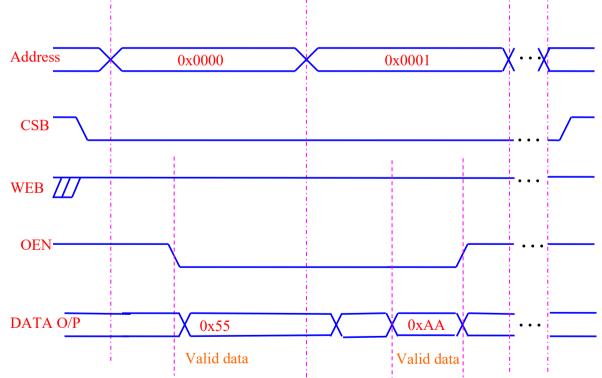

## **Switching Waveforms**

**OEN:** As per truth table: OEN = X

Fig. 2 WEB dependent Write Cycle

Fig. 3 OEN dependent Read Cycle

#### Package Details:

68 pin CQFP-J is being used to package the device. Package drawing is attached below.

#### **DISCLAIMER:**

Semi-Conductor Laboratory (SCL) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and specifications, and to discontinue any product. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

Reproduction of significant portions of SCL information in SCL data sheets is permissible only if reproduction is without alteration and is accompanied by all associated conditions, limitations, and notices. SCL is not responsible or liable for such altered documentation.