# **16-BIT TRANSCEIVER 3-STATE OUTPUT**

## (COLD SPARING, HOT INSERTION

## <u>& 5V TOLERANT INPUT)</u>

(SC1124-0)

(Radiation Tolerant)

DATA SHEET Version 1.1, Dec' 2020

Semi–Conductor Laboratory Government of India S.A.S. Nagar, Punjab-160071 www.scl.gov.in

### **PRODUCT DESCRIPTION:**

SC1124-0 16-bit Transceiver is designed for low-voltage (V<sub>DD</sub> =3.3V) operation, but with the capability to provide a TTL interface to a 5V system environment. These devices can be used as two 8-bit Transceivers or one 16-bit Transceiver. These devices provide true outputs and symmetrical active-low output-enable ( $\overline{OEB}$ ) inputs.

The A port outputs includes equivalent 22  $\Omega$  series resistors to reduce overshoot and undershoot.

Active bus-hold circuitry holds unused or undriven inputs at a valid logic state. Use of pullup or pull down resistors with the bus-hold circuitry is not recommended.

When  $V_{DD}$  is between 0 and 1.5 V, the devices are in the high-impedance state during power up or power down.

However, to ensure the high-impedance state above 1.5 V, ( $\overline{OEB}$ ) should be tied to V<sub>DD</sub> through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

These devices are fully specified for hotinsertion applications using Ioff and power-up 3state. The  $I_{OFF}$  circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down.

The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict.

### **FEATURES:**

- Operating Power Supply 3.3V ±0.3V

- Cold sparing feature at I/O

- A port outputs have equivalent 22 Ω series resistors, so no external resistors are required.

- 5V tolerant inputs for interfacing 5V logic with 3.3V  $V_{\text{DD}}$

- I<sub>OFF</sub> and power-up 3-state support hot Insertion

- Bus Hold on data inputs eliminates the need for external pull-up / pull-down resistors

- Distributed V<sub>DD</sub> and GND pins minimize high-speed switching noise

- Flow-through architecture optimizes PCB layout

- 6.0 ns typical propagation delay

- Typical V<sub>OLP</sub> (Output Ground Bounce) < 0.8 V at V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = 25°C

- Low power dissipation (<1mW at 3.6V static)

- Operating Temperature: -55°C to 125°C.

- Radiation Tolerant up to 100 KRad

- SET/SEL immune up to 50 MeV.cm<sup>2</sup>/mg

- 48 Pin CDFP /Customized package /Die

- Pin compatible with LVTH162245.

- Package  $\Theta_{JC} = 2.7^{\circ}C/Watt$

- ESD Sensitivity Level: HBM Class 1A (250V to 499V), passed up to 300V

- SCL's 180nm CMOS Technology

## RT 16-BIT TRANSCEIVER 3-STATE OUTPUT (SC1124-0)

## **PIN CONFIGURATION:**

| Pin no. | Signal | Pin no. | Signal       |

|---------|--------|---------|--------------|

| 1       | 1DIR   | 25      | 2 <i>0EB</i> |

| 2       | 1B1    | 26      | 2A8          |

| 3       | 1B2    | 27      | 2A7          |

| 4       | GND    | 28      | GND          |

| 5       | 1B3    | 29      | 2A6          |

| 6       | 1B4    | 30      | 2A5          |

| 7       | VDD    | 31      | VDD          |

| 8       | 1B5    | 32      | 2A4          |

| 9       | 1B6    | 33      | 2A3          |

| 10      | GND    | 34      | GND          |

| 11      | 1B7    | 35      | 2A2          |

| 12      | 1B8    | 36      | 2A1          |

| 13      | 2B1    | 37      | 1A8          |

| 14      | 2B2    | 38      | 1A7          |

| 15      | GND    | 39      | GND          |

| 16      | 2B3    | 40      | 1A6          |

| 17      | 2B4    | 41      | 1A5          |

| 18      | VDD    | 42      | VDD          |

| 19      | 2B5    | 43      | 1A4          |

| 20      | 2B6    | 44      | 1A3          |

| 21      | GND    | 45      | GND          |

| 22      | 2B7    | 46      | 1A2          |

| 23      | 2B8    | 47      | 1A1          |

| 24      | 2DIR   | 48      | 1 <i>0EB</i> |

| 1DIR | 1  | 48 | 028   |

|------|----|----|-------|

| 181  | 2  | 47 | 1A1   |

| 1B2  | 3  |    | 1A2   |

| GND  |    | 46 | GND   |

| 183  | 4  | 45 | 1A3   |

| 184  | 5  | 44 | 1A4   |

| VDD  | 6  | 43 | VDD   |

| 185  | 7  | 42 | 1A5   |

| 186  | 8  | 41 | 1A6   |

|      | 9  | 40 |       |

| GND  | 10 | 39 | GND   |

| 187  | 11 | 38 | 1A7   |

| 188  | 12 | 37 | 1A8   |

| 2B1  | 13 | 36 | 2A1   |

| 2B2  | 14 | 35 | 2A2   |

| GND  | 15 | 34 | GND   |

| 2B3  |    |    | 2A3   |

| 2B4  | 16 | 33 | 2A4   |

| VDD  | 17 | 32 | VDD   |

| 2B5  | 18 | 31 | 2A5   |

| 2B6  | 19 | 30 | 2A6   |

| GND  | 20 | 29 | GND   |

| 287  | 21 | 28 | 2A7   |

| 288  | 22 | 27 | 2A8   |

|      | 23 | 26 | 2028  |

| 2DIR | 24 | 25 | 202.8 |

|      |    |    |       |

Package Pin Details

Device Package View

## FUNCTIONAL TABLE:

| CONT       | ROL INPUTS | OUTPUT  | CIRCUITS      | ODEDATION       |

|------------|------------|---------|---------------|-----------------|

| <b>OEB</b> | DIR        | A PORT  | <b>B PORT</b> | OPERATION       |

| L          | L          | Enabled | Hi-Z          | B data to A bus |

| L          | н          | Hi-z    | Enabled       | A data to B bus |

| н          | х          | Hi-z    | Hi-Z          | Isolation       |

Truth table

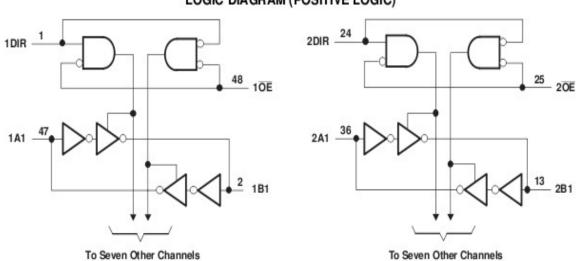

## LOGIC DIAGRAM (POSITIVE LOGIC):

LOGIC DIAGRAM (POSITIVE LOGIC)

Device Logic Diagram

## **ABSOLUTE MAXIMUM RATINGS (1):**

| Over operating free-air temperature range (unless otherwise noted), |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| PARAMETER                                                       | UNIT                                                               |

|-----------------------------------------------------------------|--------------------------------------------------------------------|

| Supply Voltage Range (V <sub>DD</sub> )                         | -0.5 V to 4.3V                                                     |

| Input Voltage Range (V <sub>IN</sub> )                          | –0.5 V to 6.5V                                                     |

| Output Voltage Range In High Impedance or Power Off $(V_{OUT})$ | -0.5 V to 4.3V                                                     |

| Output Voltage Range Applied In High State (V <sub>OUT</sub> )  | $-0.5~\mathrm{V}$ to $\mathrm{V}_{\mathrm{DD}}$ + 0.5 $\mathrm{V}$ |

| Max. Junction Temperature (T <sub>J</sub> )                     | 150°C                                                              |

| Storage Temperature Range (T <sub>STG</sub> )                   | -65°C to 150°C                                                     |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS:**

| Symbol                     | Parai                     | neter   | Min. | Тур. | Max. | Unit   |

|----------------------------|---------------------------|---------|------|------|------|--------|

| V <sub>DD</sub>            | Supply                    | voltage | 3.0  | 3.3  | 3.6  | V      |

| V <sub>IH</sub>            | High level input voltage  |         | 2.0  | -    | 5.5  | V      |

| V <sub>IL</sub>            | Low level input voltage   |         | 0    | -    | 0.8  | V      |

| T                          | High-level                | PORT A  | -    | -    | -12  | mA     |

| I <sub>он</sub>            | output current            | PORT B  | -    | -    | -24  | mA     |

| T                          | Low-level                 | PORT A  | -    | -    | 12   | mA     |

| I <sub>OL</sub>            | output current            | PORT B  | -    | -    | 24   | mA     |

| $\Delta t / \Delta V_{DD}$ | Power up ramp rate        |         | 200  | -    | -    | usec/V |

| T <sub>A</sub>             | Ambient Temperature range |         | -55  | -    | 125  | °C     |

## **DC ELECTRICAL SPECIFICATIONS:**

Table below shows eelectrical test conditions, test limits and typical measured values.

| Symbol           | Paramete                            | r            | Test Conditions                                                                                                  |                                                  | Test Conditions |      | Test Conditions |                       | V <sub>DD</sub> | Т | est Limi | ts | Units |

|------------------|-------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|------|-----------------|-----------------------|-----------------|---|----------|----|-------|

| Symbol           | 1 ai amete                          |              | 103                                                                                                              | • 00                                             | MIN.            | ТҮР. | MAX.            | Onits                 |                 |   |          |    |       |

|                  |                                     |              | $V_{IN} = V_{SS} \text{ or } V_{DD}$                                                                             |                                                  | 3.6V            | -    | -               | ±1                    | μA              |   |          |    |       |

| -                |                                     | Control Pins |                                                                                                                  | $V_{IN} = 5.5V$                                  |                 | -    | -               | ±10                   | pri i           |   |          |    |       |

| I <sub>IN</sub>  | Input Current                       |              |                                                                                                                  | = 0V or 5.5V                                     | 0V              |      | -               | ±10                   |                 |   |          |    |       |

|                  |                                     | A or B Ports |                                                                                                                  | $= V_{SS} \text{ or } V_{DD}$                    | 3.6V            | -    | -               | $\pm 5$<br>$\pm 10$   | μA              |   |          |    |       |

| I <sub>IN</sub>  | Input Bus Hold                      |              |                                                                                                                  | $V_{\rm IN} = 5.5 V$<br>= $V_{\rm IL} = 0.8 V$   |                 | -    | - 120           | $\pm 10$<br>$\pm 200$ | μΑ              |   |          |    |       |

| (hold)           | Current                             | A or B Ports |                                                                                                                  | $V_{\rm IL} = 0.8V$<br>= $V_{\rm IH} = 2.0V$     | 3.0V            | -    | -147            | $\pm 200$             | μA<br>μA        |   |          |    |       |

|                  |                                     | A Port       | $V_{IH} = 2V$                                                                                                    | $I_{OH} = -100 uA$                               | 3.0V            | 2.8  | 2.99            | -                     |                 |   |          |    |       |

| V                | High Level output                   |              |                                                                                                                  | $I_{OH} = -12mA$                                 |                 | 2.0  | 2.43            | -                     | 17              |   |          |    |       |

| V <sub>OH</sub>  | Voltage                             | D Dout       | $\mathbf{V} = 2\mathbf{V}$                                                                                       | $I_{OH} = -100uA$                                | 2 01/           | 2.8  | 2.97            | -                     | V               |   |          |    |       |

|                  |                                     | B Port       | $V_{IH} = 2V$                                                                                                    | $I_{OH} = -8mA$                                  | 3.0V            | 2.4  | 2.74            | -                     |                 |   |          |    |       |

|                  |                                     |              |                                                                                                                  | $I_{OH} = -24mA$ $I_{OL} = 100uA$                |                 | 2.0  | 2.38<br>0.003   | - 0.2                 |                 |   |          |    |       |

|                  |                                     | A Port       | $V_{IL} = 0.8V$                                                                                                  | $I_{OL} = 100 \text{uA}$ $I_{OL} = 12 \text{mA}$ | 3.0V            | -    | 0.003           | 0.2                   |                 |   |          |    |       |

| V <sub>OL</sub>  | Low Level output                    |              |                                                                                                                  | $I_{OL} = 100 \text{uA}$                         |                 | _    | 0.005           | 0.8                   | V               |   |          |    |       |

| ▼ OL             | Voltage                             | B Port       | $V_{IL} = 0.8V$                                                                                                  | $I_{OL} = 12mA$                                  | 3.0V            | _    | 0.005           | 0.2                   | v               |   |          |    |       |

|                  |                                     | DIOR         | VIL 0.0V                                                                                                         | $I_{OL} = 24 \text{mA}$                          | 5.0 V           | _    | 0.641           | 0.8                   |                 |   |          |    |       |

| T                | Three-State Output                  | A Port       | $\overline{OEB} = \text{Disabled}$ $V_{O} = 3V$                                                                  |                                                  | 3.6V            | -    | -               | ±5                    | A               |   |          |    |       |

| I <sub>OZH</sub> | Leakage Current High                | B Port       |                                                                                                                  |                                                  | 3.0 V           | -    | -               | ±3                    | μA              |   |          |    |       |

| T                | Three-State Output                  | A Port       | $\overline{OEB} = \text{Disabled}$                                                                               |                                                  |                 | -    | -               |                       |                 |   |          |    |       |

| I <sub>OZL</sub> | Leakage Current Low                 | B Port       | $V_0 = 0.5V$                                                                                                     |                                                  | 3.6V            | -    | -               | $\pm 5$               | μA              |   |          |    |       |

| I <sub>OFF</sub> | Power Off Input<br>Leakage Current  | A or B Ports | $V_I = 0V \text{ or } 4.5V$                                                                                      |                                                  | 0V              | -    | -               | ±50                   | μΑ              |   |          |    |       |

| IOFF             | Power Off Output<br>Leakage Current | A or B Ports | V <sub>o</sub> =                                                                                                 | = 0V or 4.5V                                     | 0V              | -    | -               | ±50                   | μΑ              |   |          |    |       |

|                  |                                     |              | $V_{IN} = V_{DD}$                                                                                                | Outputs High                                     |                 | -    | 0.140           |                       |                 |   |          |    |       |

|                  |                                     | A Port I/P   |                                                                                                                  | Outputs Low                                      |                 | -    | 0.139           |                       |                 |   |          |    |       |

|                  | Static Supply Current               |              | or V <sub>SS</sub>                                                                                               | Outputs Disabled                                 | 3.3±            | -    | 0.139           | 0.25                  | mΛ              |   |          |    |       |

| I <sub>DD</sub>  | (No Load, Iout =0A)                 |              | $V_{IN} = V_{DD}$                                                                                                | Outputs High                                     | 0.3V            | -    | 0.140           | 0.23                  | mA              |   |          |    |       |

|                  |                                     | B Port I/P   |                                                                                                                  | Outputs Low                                      |                 | -    | 0.136           |                       |                 |   |          |    |       |

|                  |                                     |              | or V <sub>SS</sub> Outputs Disa                                                                                  |                                                  |                 | -    | 0.139           |                       |                 |   |          |    |       |

| $\Delta I_{DD}$  | Static Supply Current               | A Port       | One input at $V_{DD} - 0.6V$                                                                                     |                                                  | 3.0 V<br>and    | -    | 24.9            | 100                   | uA              |   |          |    |       |

|                  | delta                               | B Port       | Other input at $V_{DD}$ or $V_{SS}$                                                                              |                                                  | 3.6 V           | -    | 24.3            | 100                   | ]               |   |          |    |       |

| Ras              | ic Functional Test                  | A Port       | $\label{eq:VIL} \begin{array}{c} V_{IL}{=}0.8V, V_{IH}{=}2.0V \\ V_{OL}{\leq}0.4V, V_{OH}{\geq}2.4V \end{array}$ |                                                  | $3.3 \pm$       | _    | _               | 1                     | Mhz             |   |          |    |       |

|                  |                                     | B Port       |                                                                                                                  |                                                  | 0.3V            |      | _               | 1                     | IVIIIZ          |   |          |    |       |

| Functio          | onal Test 5V Tolerant               | A Port       | $V_{IL}=0V, V_{IH}=5.5V$                                                                                         |                                                  | 3.0V            | _    | -               | 1                     | Mhz             |   |          |    |       |

|                  |                                     | B Port       | $V_{OL} \leq 0.4 V, V_{OH} \geq 2.4 V$                                                                           |                                                  |                 |      |                 |                       |                 |   |          |    |       |

DC Electrical Specification

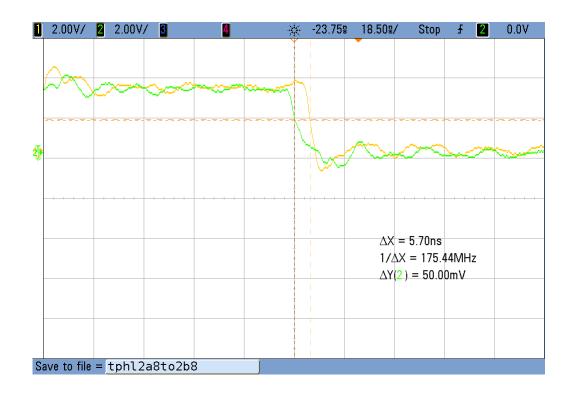

## AC ELECTRICAL SPECIFICATIONS:

## **Test condition:**

$V_{DD}{=}3.3V,\,V_{IN}{=}\,0V$  or 3.3V @1 MHz,  $R_L{=}500\Omega$  ,  $C_L{=}50pF,\,T_A{=}22\pm3^\circ C$

| Danamatan        | Enom       | Та | $V_{DD} = 3.3 V$ |      |      | I.I.a.:4a |    |

|------------------|------------|----|------------------|------|------|-----------|----|

| Parameter        | From       | То | Min.             | Тур. | Max. | Units     |    |

| t <sub>PLH</sub> | A          | В  | -                | 5.23 | 10   | ns        |    |

| t <sub>PHL</sub> | A          | Б  | -                | 5.30 | 10   | ns        |    |

| t <sub>PLH</sub> | В          |    | -                | 6.24 | 10   | ns        |    |

| t <sub>PHL</sub> | D          | А  | -                | 6.31 | 10   | ns        |    |

| t <sub>PZH</sub> |            |    | -                | 5.22 | -    | ns        |    |

| t <sub>PZL</sub> | <u> </u>   | В  | -                | 4.86 | -    | ns        |    |

| t <sub>PHZ</sub> |            | D  | -                | 4.16 | -    | ns        |    |

| t <sub>PLZ</sub> | ]          |    | -                | 4.68 | -    | ns        |    |

| t <sub>PZH</sub> |            |    | -                | 5.74 | -    | ns        |    |

| t <sub>PZL</sub> | <u>OEB</u> |    | А                | -    | 5.20 | -         | ns |

| t <sub>PHZ</sub> |            | A  | -                | 5.02 | -    | ns        |    |

| t <sub>PLZ</sub> | ]          |    | -                | 5.51 | -    | ns        |    |

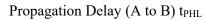

## **TEST CIRCUIT AND SWITCHING WAVEFORM:**

AC parameter measurement information

#### NOTES:

A: CL includes probe and jig capacitance

B: Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

## **COLD SPARING (IOFF) TEST:**

In cold sparing I/O when  $V_{DD}$  is down to zero volt, I/Os will go in the high-impedance state so that damage to the device does not occur.

Ioff protection circuitry ensures that no excessive current is drawn from or to an input, output, or combined I/O that is biased to a specified voltage while the device is powered down. This condition can occur when subsections of a system are powered down (partial power down) to reduce energy consumption. All standard logic devices with the I<sub>OFF</sub> specification allow only 100 uA of maximum current. Any current in excess of this amount (for example, a forward-biased p-n junction) is not considered normal leakage current.

## PU3S (Power Up Tri State) HOT INSERTION TEST:

Testing of power-up three-state (PU3S) circuits was done at nominal temperature and voltage. All devices tested have a nominal  $V_{DD}$  of 3.3 V.

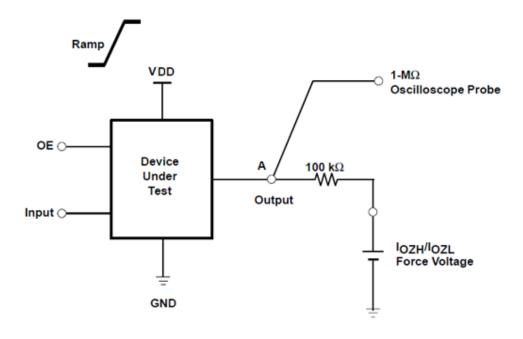

The test setup is shown below. The  $V_{DD}$  was ramped at ramp rate (> 200usec / V) to determine the effect of the  $V_{DD}$  ramp rate on the device output or I/O structure. I<sub>O</sub> was not measured directly; instead the voltage was measured at the output or I/O terminal (terminal A in Figure 1) with a 1-M $\Omega$  oscilloscope probe.

Test circuit (PU3S)

## HOT INSERTION TEST

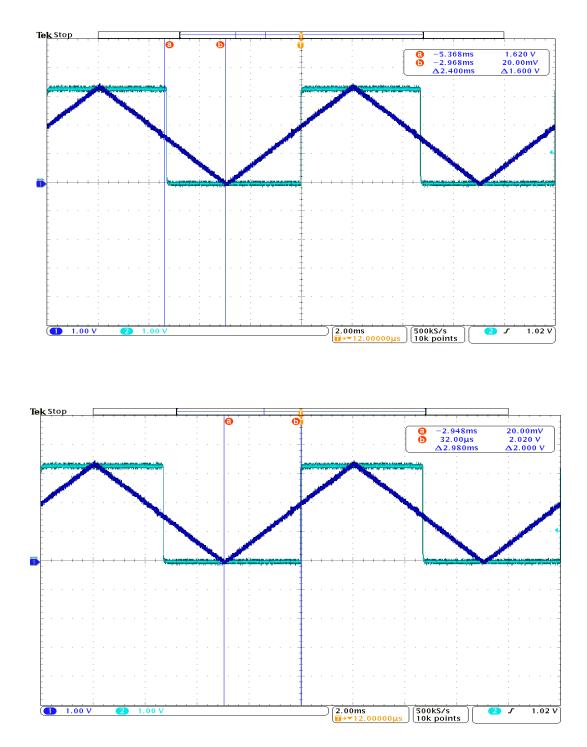

**Conditions:**  $\overline{OEB}$  = LOW (Enable), I/P = Low (0V), O/P = 3.3V through 1K $\Omega$  resistor

$V_{\text{OZH}}$  at supply  $V_{\text{DD}}$  (ramp rate: 1msec/V), O/P is in HighZ with  $V_{\text{DD}}$  <1.5V

## **<u>GROUND BOUNCE AND VDD</u> BOUNCE:** (MIL-STD-883E METHOD 3024)

- A. **Ground bounces noise:** The voltage amplitude (peak) of extraneous signals present on a low-level non-switching output with a specified number of other outputs switching. Ground bounce noise on a logic low output can be of sufficient amplitude to exceed the high level threshold of a receiver, or cause latch-up on unprotected CMOS inputs.

- B.  $V_{DD}$  bounce noise: The voltage amplitude (peak) of extraneous signals present on a highlevel non-switching output with a specified number of other outputs switching. VCC bounce on a logic high output can be of sufficient amplitude to exceed the low level threshold of a receiver, or cause latch-up on unprotected CMOS inputs.

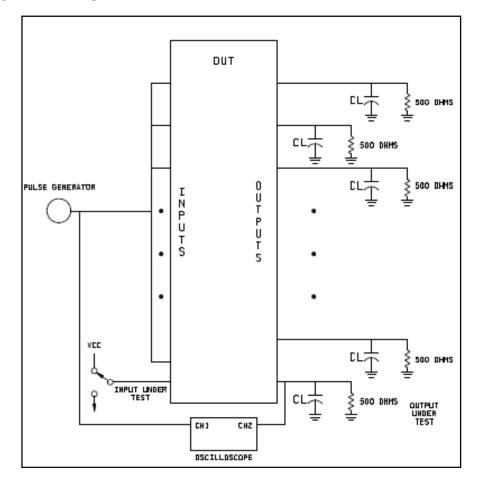

Ground bounce and  $V_{\text{DD}}$  bounce tests were done at nominal temperature and voltage.

All devices tested have a nominal  $V_{DD}$  of 3.3 V. The output condition for pin under test is to a low level for Ground bounce and to a high level for  $V_{DD}$  bounce test and the other outputs were switching. The test setup is shown below;

Test Circuit (Ground /VDD Bounce)

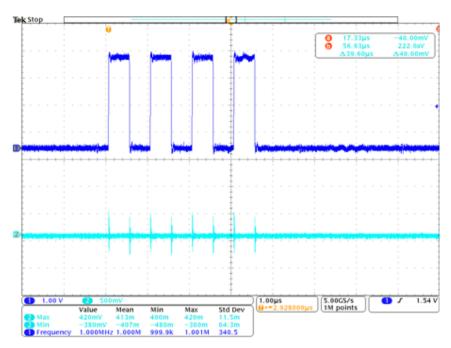

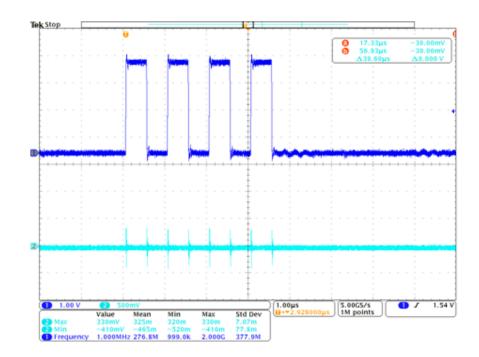

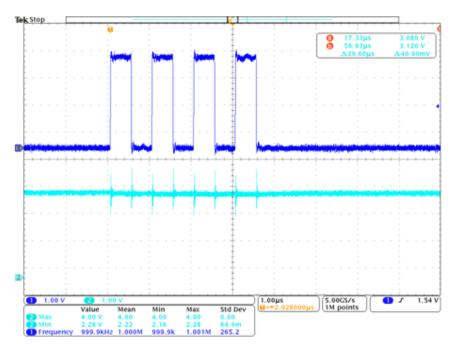

## **GROUND BOUNCE TEST:**

**Conditions:**  $\overline{OEB}$  = LOW (Enable), I/P corresponding to output under test = Low (0V), other inputs = Switching, O/P under test = through 500 $\Omega$  resistor

i) Direction: A to B

ii) Direction: B to A

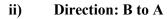

## **V**<sub>DD</sub> BOUNCE TEST:

**Conditions:**  $\overline{OEB}$  = LOW (Enable), I/P corresponding to output under test = High (3.3V), other inputs = Switching, O/P under test = through 500 $\Omega$  resistor

i) Direction: A to B

## **RADIATION CHARACTERISTICS:**

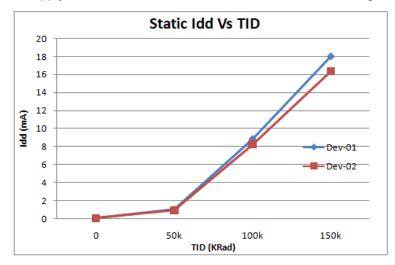

## **\*** Total Ionization Dose (TID) Testing

- TID testing of 16 Bit Transceiver (SC1124-0) is performed for radiation level up to 150 KRad.

- No functional degradation and no significant change in device parameters such as IIL, IIH, VOL & VOH was observed up to 100KRad.

- > Static supply current increases with radiation dose, shown in figure below.

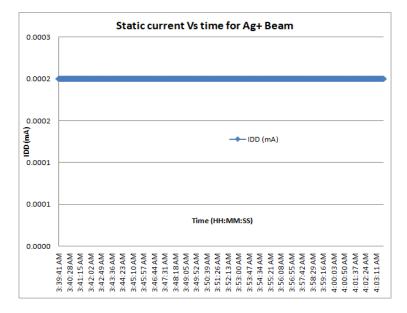

## ✤ Single Event Effect (SEE) Testing

SEE testing of 16 Bit Transceiver (SC1124-0) is performed at two different LET energy ion beams Ti+ (20 MeV-cm2/mg) and Ag+ (50 MeV-cm2/mg) for a Fluence of 10<sup>6</sup> ions/cm<sup>2</sup>.

- No Single Event latch-up (SEL) was observed up to LET of 50 MeV-cm2/mg. Supply current (I<sub>DD</sub>) remains within specification throughout testing.

- > No Single Event transient (SET) was observed up to LET of 50 MeV-cm2/mg.

## **REVISION HISTORY**

| S. No. | Version | Date of release             | Description |

|--------|---------|-----------------------------|-------------|

| 1      | 1.0     | 26 <sup>th</sup> March 2019 | New         |

| 2      | 1.1     | December 2020               | Revised     |

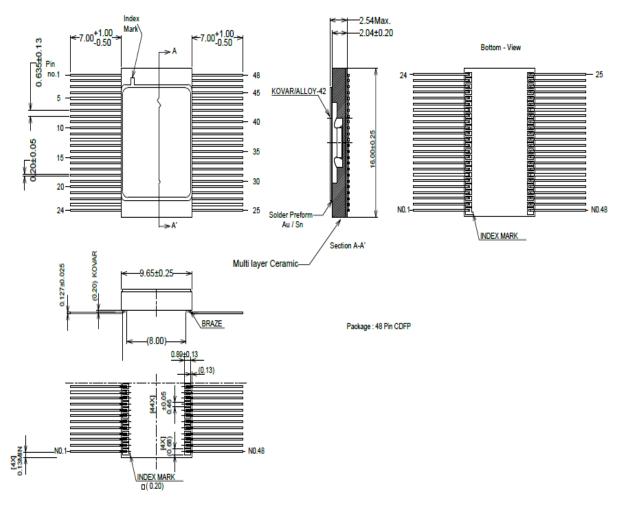

## PACKAGE DRAWING (48 Pin Ceramic Dual Flat Pack):

NOTE: All linear dimensions are in inches (mm.)

#### DISCLAIMER

Semi Conductor Laboratory (SCL) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and specifications, and to discontinue any product. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Reproduction of significant portions of SCL information in SCL data sheets is permissible only if reproduction is without alteration and is accompanied by all associated conditions, limitations, and notices. SCL is not responsible or liable for such altered documentation.