# **Operational Amplifier**

## (SC1403-0)

**DATA SHEET** *Version 1.0, Dec' 2015*

Semi–Conductor Laboratory Government of India S.A.S. Nagar, Punjab-160071 www.scl.gov.in

#### **PRODUCT DESCRIPTION:**

SC1403-0 is an op amp that is designed as an IP block. This chip consists of 2 nos. of internally compensated CMOS input op-amps in folded cascade architecture. First op-amp has internal bias resistor whereas second op-amp requires approx.  $33k\Omega$  external bias resistor with V<sub>DD</sub>.

#### **FEATURES:**

- Operating Supply Voltage: 3.0V± 0.3V

- Open loop Gain > 80db

- Settling Time (0.05%) < 40ns

- Unity Gain Bandwidth > 20MHz

- Power Dissipation < 15mW

- Load Resistance > 1KΩ

- Load Capacitance < 30pF

- Operating Temperature: -55°C to 125°C

- Ceramic 16-pin DIP packages

| 1 | CHIP_OUT  | NC                     | 16 |

|---|-----------|------------------------|----|

| 2 |           |                        | 15 |

| 3 |           | NC<br>NC               | 14 |

| 4 |           | NC                     | 13 |

| 5 | CHIP_VSS  |                        | 12 |

| 6 | NC        | CHIP_OUT1<br>CHIP_VDD1 | 11 |

| 7 | CHIP_VSS1 | CHIP_BIAS              | 10 |

| 8 | CHIP_INP1 | CHIP INN1              | 9  |

|   |           |                        |    |

#### **DEVICE PIN DIAGRAM:**

#### **DEVICE PIN DESCRIPTION:**

| DIE – 1       |          |                     | DIE – 2 |           |                     |

|---------------|----------|---------------------|---------|-----------|---------------------|

| Pin No.       | Pin Name | Description         | Pin No. | Pin Name  | Description         |

| 1             | CHIP_OUT | Output              | 7       | CHIP_VSS  | Supply Ground       |

| 2             | CHIP_VDD | Supply Power        | 8       | CHIP_INP  | Non-inverting Input |

| 3             | CHIP_INN | Inverting Input     | 9       | CHIP_INN  | Inverting Input     |

| 4             | CHIP_INP | Non-inverting Input | 10      | CHIP_BIAS | Bias Resister (33K) |

| 5             | CHIP_VSS | Supply Ground       | 11      | CHIP_VDD  | Supply Power        |

| 6,13,14,15,16 | NC       | Not connected       | 12      | CHIP_OUT  | Output              |

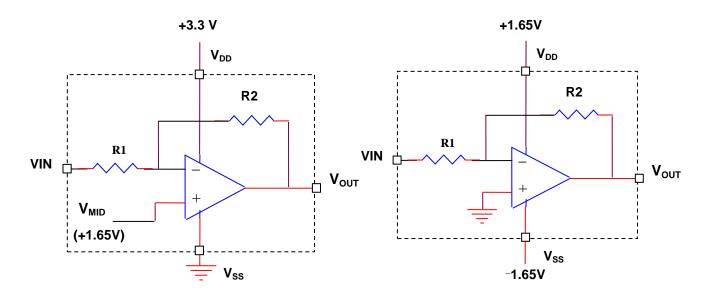

#### OP AMP IN SINGLE SUPPLY AND DUAL SUPPLY CONFIGURATION:

#### **RECOMMENDED OPERATING CONDITIONS:**

| SYMBOL                                         | PARAMETER                                          | Min | Max      | Unit |

|------------------------------------------------|----------------------------------------------------|-----|----------|------|

| V <sub>DD</sub>                                | Supply Voltage                                     | 3.0 | 3.6      | V    |

| V <sub>IN</sub>                                | IN Input Voltage Range                             |     | $V_{DD}$ | V    |

| I <sub>OH</sub>                                | I <sub>OH</sub> High level output current (Source) |     | -0.8     | mA   |

| I <sub>OL</sub>                                | I <sub>OL</sub> Low level output current (Sink)    |     | 12       | mA   |

| T <sub>AMB</sub> Operating Ambient Temperature |                                                    | -55 | 125      | °C   |

### ABSOLUTE MAXIMUM RATINGS (1):

Over operating free-air temperature range (unless otherwise noted),

| Symbol                              | Parameter                 | Unit                                        |

|-------------------------------------|---------------------------|---------------------------------------------|

| V <sub>DD</sub>                     | Supply Voltage Range      | -0.5V to 4.3V                               |

| V <sub>IN</sub> Input Voltage Range |                           | –0.5V to $V_{\text{DD}}\text{+}0.5\text{V}$ |

| T <sub>J</sub>                      | Max. Junction Temperature | 150°C                                       |

| TstgStorage Temperature Range       |                           | –65°C to 150°C                              |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## DC ELECTRICAL SPECIFICATIONS:

$@V_{dd} = \pm 1.65V, V_{CM}=0V, T_A = 25^{\circ}C$

| Specifications                 | Symbol                     | Test Inputs                               | Test Conditions                               | Test Results<br>(Typ.) | Unit  |

|--------------------------------|----------------------------|-------------------------------------------|-----------------------------------------------|------------------------|-------|

| INPUT CHARACTE                 | RISTICS                    |                                           |                                               |                        |       |

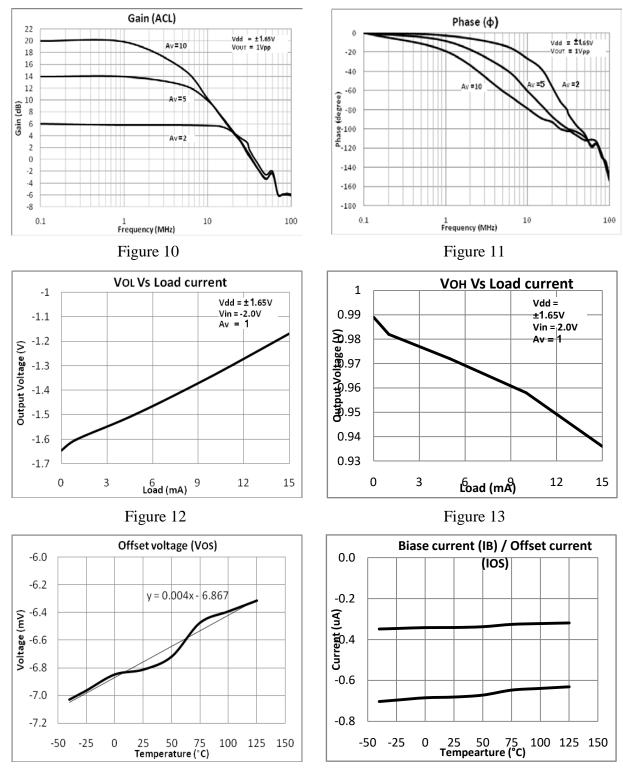

| Input Offset V <sub>OS</sub>   |                            |                                           |                                               | -6.70                  | mV    |

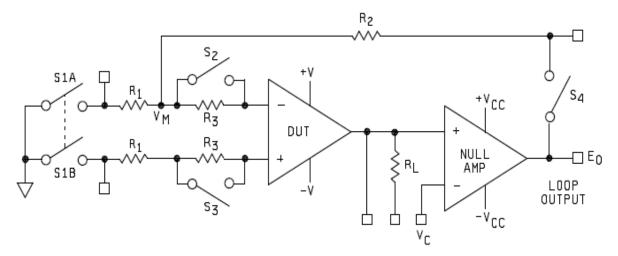

| Input Offset<br>Current        | I <sub>OS</sub>            | Test Method 4001.1<br>(Table - 5)         | R2/R1 = 30K/100<br>R3 = 10K<br>Test Circuit-1 | 0.664                  | μA    |

| Input Bias<br>Current          | I <sub>IB</sub>            |                                           |                                               | 0.355                  | μA    |

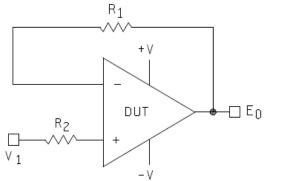

| Input Voltage                  | VIH                        | VIN+ (RAMP) = 3.6Vpp                      | G = +1                                        | 0.935                  | V     |

| Range (ICMR)                   | V <sub>IL</sub>            | (f = 100Khz)                              | Test Circuit-2                                | -1.586                 | V     |

| Common Mode<br>Rejection Ratio | CMRR                       | Test Method 4003.1                        | R2/R1 = 30K/100                               | 34.41                  | dB    |

| Large Signal<br>Voltage Gain   | A <sub>OL</sub>            | Test Method 4004.1                        | Test Circuit-1                                | 83.52                  | dB    |

| Offset Voltage<br>Drift        | $\Delta V_{OS} / \Delta T$ | Test Method 4001.1                        | -40°C to 125°C                                | 4.0                    | µV/⁰C |

| OUTPUT CHARAC                  | TERISTICS                  |                                           |                                               |                        |       |

| Output                         | VOU                        | Vdd = ±1.65V                              | IL = 1mA, ACL = 1                             | 0.982                  | V     |

| Voltage High                   | VOH                        |                                           | IL = 10mA, ACL = 1                            | 0.958                  | V     |

| Output                         |                            | VIN+ (DC) = 2.0V                          | IL = 1mA, ACL = 1                             | -1.647                 | V     |

| Voltage Low                    | VOL                        |                                           | IL = 10mA, ACL = 1                            | -1.338                 | V     |

| Output Short                   | I <sub>OUT+</sub> (source) | Vdd = ±1.65V<br>V <sub>IN+</sub> = 1.65V  | G = +1                                        | 31.36                  | mA    |

| Circuit Current                | I <sub>OUT-</sub> (sink)   | Vdd = ±1.65V<br>V <sub>IN+</sub> = -1.65V | o/p short with GND<br>Test Circuit-2          | 30.65                  | mA    |

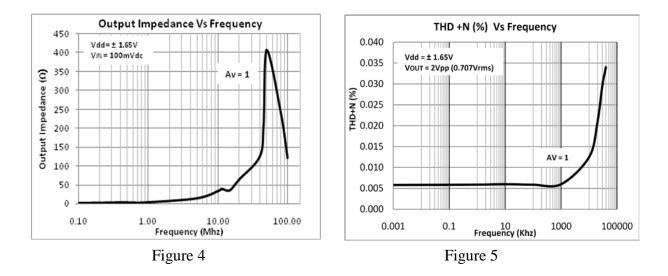

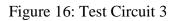

| Output<br>Impedance            | Z <sub>OUT</sub>           | f = 50Mhz                                 | f = 50Mhz Test circuit 4                      |                        | Ohm   |

| Output<br>Resistance           |                            |                                           | Test circuit 4                                | 0.05                   | Ohm   |

| POWER SUPPLY                   | Γ                          |                                           |                                               |                        |       |

| Supply Current                 | Idd                        | $Vdd = \pm 1.65V$                         | G = +1<br>Test Circuit-2<br>(No Load)         | ± 4.2                  | mA    |

| Power<br>Dissipation           | Pd                         | V <sub>OUT</sub> = 0V                     |                                               | 14.0                   | mW    |

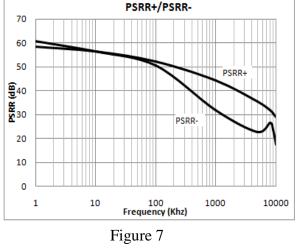

| PSRR                           | PSRR+                      | Vdd+ =1.65 ± 0.165V<br>Vdd- = -1.65V      | Test Circuit-1                                | -53.14                 | dB    |

| FORA                           | PSRR-                      | Vdd+ = 1.65V<br>Vdd- = -1.65 ± 0.165V     |                                               | -53.89                 |       |

## AC ELECTRICAL SPECIFICATIONS:

$@V_{dd} = \pm 1.65V, V_{CM}=0V, T_A = 25^{\circ}C$

| Specifications                      | Symbol                                                                  | Test Inputs                                                         | Test Conditions                               | Test Results (Typ.) | Unit   |  |

|-------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|---------------------|--------|--|

| DYNAMIC CHARACTERISTICS             |                                                                         |                                                                     |                                               |                     |        |  |

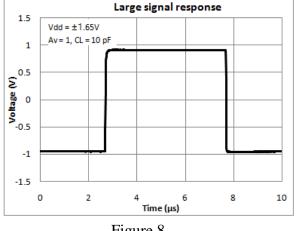

| Slew Rate<br>(Rise)                 | SR+                                                                     |                                                                     |                                               | 70                  | V/us   |  |

| Slew Rate<br>(Fall)                 | SR-                                                                     | Vdd+ = 1.65V<br>Vdd- = -1.65V<br>VIN+ (SQUARE) = 3Vpp<br>(f = 1Mhz) | G = +1<br>RL = 10K<br>Test Circuit-2          | 74                  | V/us   |  |

| Full Power<br>Bandwidth             | FPBW                                                                    | (1 = 10002)                                                         |                                               | 11                  | MHz    |  |

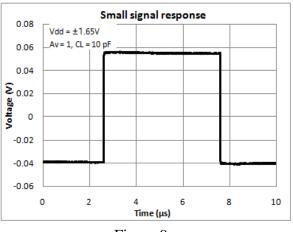

| Gain<br>Bandwidth<br>Product        | GBP                                                                     | VOUT(SINE) = 400mVpp<br>(freq sweep)                                | G = +1<br>Test Circuit-2                      | 50                  | MHz    |  |

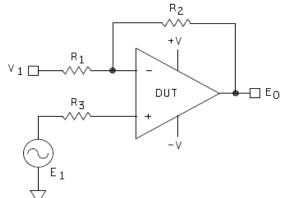

| Unity Gain<br>Bandwidth             | UGB                                                                     | VIN+(SINE) = 100mVpp<br>(freq sweep)                                | R2/R1 = 9K/1K<br>VIN = VOUT<br>Test Circuit-3 | 32                  | MHz    |  |

| Settling Time<br>to 0.05%<br>(Rise) | TSS                                                                     | VOUT = 1V STEP                                                      | G = +1, RL = 1K ,<br>CL = 30pF                | 65                  | nsec   |  |

| Phase Margin                        | Phase Margin $\phi M$ $Vdd = \pm 1.65 V$<br>VOUT(SINE) = 1 Vpp $G = +1$ |                                                                     | G = +1                                        | 80                  | Degree |  |

| NOISE PERFORMANCE                   |                                                                         |                                                                     |                                               |                     |        |  |

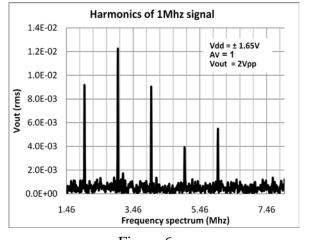

| Total<br>Harmonic                   | THD + N                                                                 | VOUT = 1V STEP                                                      | G = +1                                        | 0.006               | %      |  |

| Distortion<br>+ Noise               | F = 1 Mhz                                                               | -84.44                                                              | dB                                            |                     |        |  |

Table 3

## TYPICAL CHARACTERISTICS:

Figure 8

Figure 13

## **TEST METHOD:**

| S.N. | Test                                    | Test method (MIL-STD-883E) | Test circuit   |

|------|-----------------------------------------|----------------------------|----------------|

| 1    | Input offset voltage (V <sub>IO</sub> ) | Method 4001.1              | Test circuit 1 |

| 2    | Input offset current (I <sub>IO</sub> ) | Method 4001.1              | Test circuit 1 |

| 3    | Input bias current $(I_{IB})$           | Method 4001.1              | Test circuit 1 |

| 4    | CMMR                                    | Method 4003.1              | Test circuit 1 |

| 5    | +PSRR/ -PSRR                            | Method 4003.1              | Test circuit 1 |

| 6    | Open Loop Gain                          | Method 4004.1              | Test circuit 1 |

| 7    | Slew Rate (S.R.)                        | Method 4002.1              | Test circuit 2 |

| 8    | Phase Margin                            | Method 4002.1              | Test circuit 2 |

| 9    | FPBW                                    | Method 4002.1              | Test circuit 2 |

| 10   | UGB                                     | Method 4004.1              | Test circuit 3 |

| 12   | Output Impedance                        | Method 4005.1              | Test circuit 4 |

| 13   | Power Dissipation                       | Method 4005.1              | Test circuit 4 |

| 14   | ICMR                                    |                            | Test circuit 2 |

| 15   | VOH/VOL                                 |                            | Test circuit 2 |

| 16   | +I <sub>SC</sub> / -I <sub>SC</sub>     |                            | Test circuit 2 |

Table 5

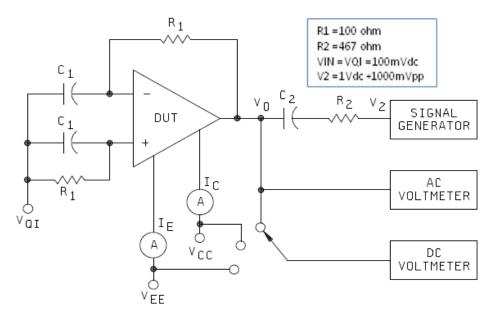

**TEST CIRCUITS:**

Figure 14: Test Circuit 1

Figure 15: Test Circuit 2

Figure 17: Test Circuit 4

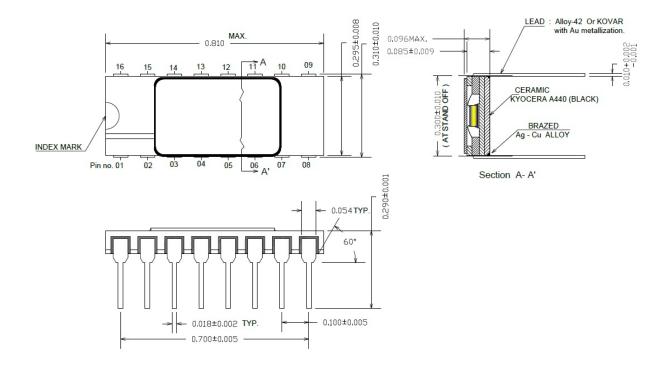

#### **MECHANICAL PACKAGE DRAWING:**

#### **16 PIN DIP PACKAGE**

#### **IMPORTANT NOTICE**

Semi Conductor Laboratory (SCL) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and specifications, and to discontinue any product. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Reproduction of significant portions of SCL information in SCL data sheets is permissible only if reproduction is without alteration and is accompanied by all associated conditions, limitations, and notices. SCL is not responsible or liable for such altered documentation.